Optimizing Decoupling Capacitors

- Posted by doEEEt Media Group

- On June 24, 2022

- 0

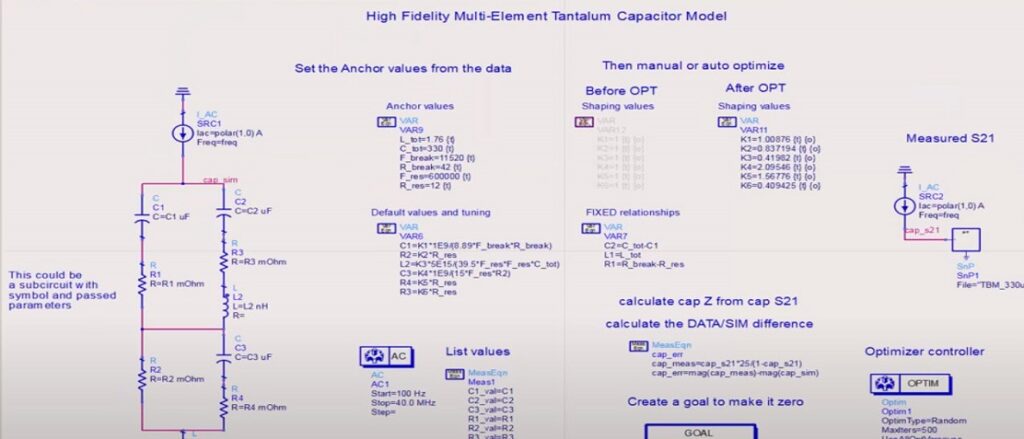

Learn how to optimize decoupling capacitors for the best cost vs. performance using flat target impedance design methods.

Impedance peaks caused by parallel L-C resonances in the power distribution network (PDN) are potential sources of power rail ripple and increased EMI. Bulk capacitors must be selected to ensure power supply stability while high-frequency decoupling must ensure the required bandwidth at the Load.

Simple SPICE simulations fail to account for PCB parasitics and often result in the wrong selection of decoupling capacitors. Utilizing EM models of the PDN and combining them with power supply state-space models and the spectral requirements of the load result in good agreement with measurements.

Optimizing this PDN ecosystem shows that designing for flat impedance is the best way to achieve the lowest noise on the power rail with the minimum number of capacitors.

Source: Picotest

- Space-Grade components available for immediate delivery - April 10, 2025

- Managing EEE components for LEO and lower cost space missions - December 17, 2024

- Filtering Characteristics of Parallel-Connected Fixed Capacitors in LCC-HVDC - November 21, 2024

0 comments on Optimizing Decoupling Capacitors