Introduction to Ceramic Capacitors

- Posted by doEEEt Media Group

- On July 1, 2020

- 0

INTRODUCTION to CERAMIC CAPACITORS

Within the electrostatic capacitor family, we can distinguish two groups: the organic film capacitors described on the foregoing pages and capacitors with inorganic dielectrics. Of these dielectrics, we will start with the dominating ceramic materials.

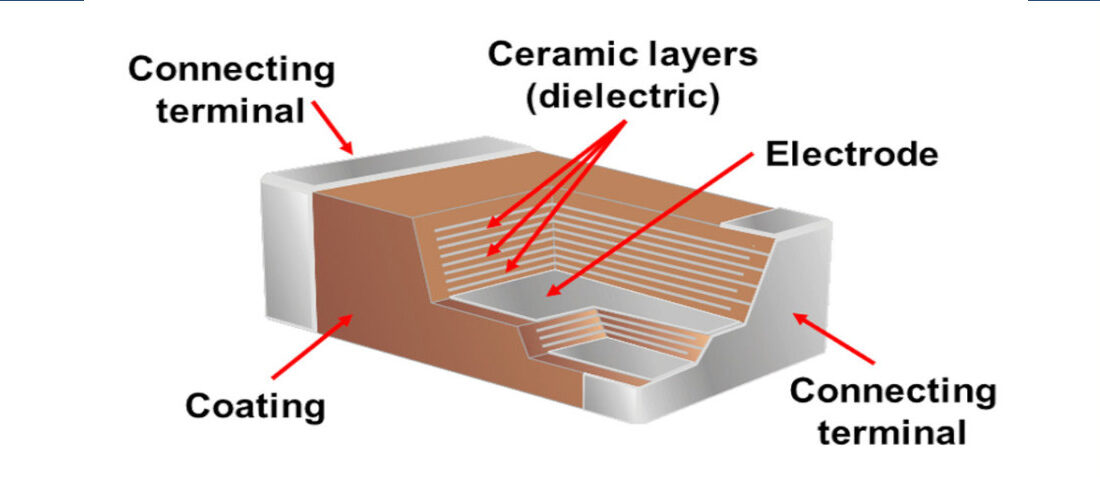

Construction

The capacitors consist, as the name tells us, of some kind of ceramic. The manufacturing process starts with a finely grounded ceramic powder mixed to an emulsion of solvents and resin binders. In the first manufacturing step, the emulsion then is dried to a soft film and screen printed with an electrode paste, historically it was a compound of palladium or silver and palladium + binding agents. Due to the high cost of palladium, this termination style was replaced by metals like copper and nickel, so-called base metal electrodes (BME) that is a majority of today’s MLCC designs.

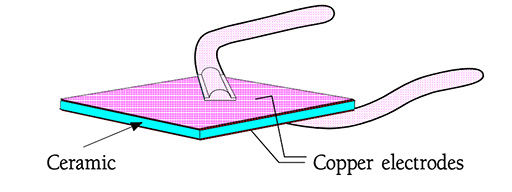

So-called tube capacitors are extruded out of a nozzle and are covered with an electrode paste on the inside and the outside before it’s sintered to its definite material structure. In the same way, the Single Layer Ceramic Capacitor (SLCC) consists of one dielectric layer. The ceramic is covered with an adhesive layer of, for example, chrome nickel as a base for copper electrodes. On the electrodes, leads are soldered as shown in principle Figure 1, before the component is encapsulated in lacquer or epoxy.

Find in doEEEt all the capacitors you need for your design, and navigate in the biggest online database for Ceramic capacitors for free

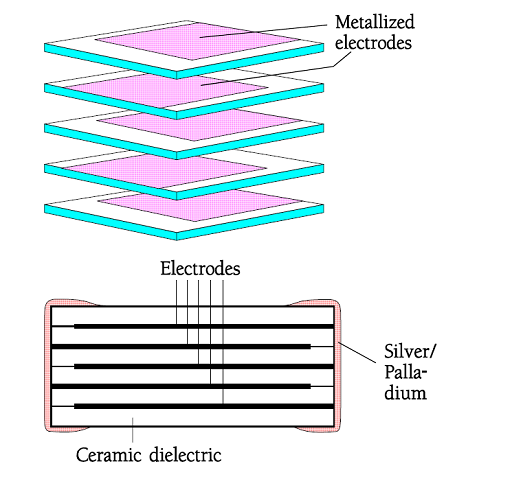

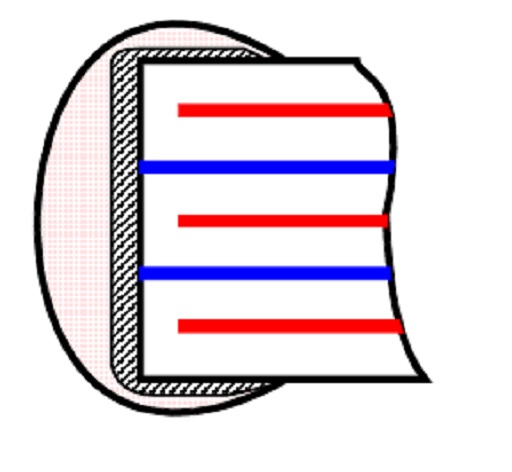

The most common design of a ceramic capacitor is the multilayer construction where the capacitor elements are stacked as shown in Figure 2, so-called MLCC (Multi-Layer Ceramic Capacitor). The number of layers has to be limited for reasons of the manufacturing technique. The upper limit amounts at present to over 1000. Besides economic reasons come into play. Where expensive noble metals in the electrode paste are used they raise the price steeply at higher capacitance values. The lowest capacitance values are achieved by only two layers, often separated by double ceramic layers.

In the conventional so-called the dry method the ceramic emulsion is dried on a conveyor belt before it is separated from the supporting bed. After it is cut into “primary sheets” that are screen printed with electrode paste for a large number of chips. These primary sheets then are stacked in an accurate steel frame and pressed to a solid piece in order to make it possible to cut out the separate chips from the stack with the electrodes in alternating positions as shown in Figure 2 below.

In the latest variant of this method, one utilizes a conveyor film for the ceramic emulsion and has thus succeeded in reducing the dielectric thickness to 3 μm (0.1 mil). Here the quality implies manufacture in extremely “clean rooms”, i.e. in rooms with filtered air and control of the number and size of particles.

Before the variant with a conveyor film was used in the dry method, the so-called wet method was becoming more and more common. There the stage with the handling of “primary sheets” is skipped by letting the emulsion dry in “primary sheet frames”. In combination with better milling methods for the ceramic powder and a higher material purity, the wet method makes it possible with thinner dielectrics without a growing failure rate.

Figure 2. MLC capacitor with AgPd terminals

The separate cut loose chips are subjected to a first heat treatment (burn-out) where the organic binding agents – also those being part of the electrode paste – are gasified and diffuse through the not yet sintered ceramic. If this process is forced too fast gas bubbles are formed that will separate electrodes and ceramics and results in so-called delaminations (Figure 3).

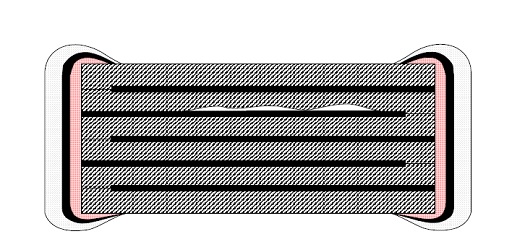

Figure 3. Schematic of delamination.

The risk with delamination also increases with the number of layers. Primarily it depends on the quantity of electrode metal in the ceramic and the differences in TCE (coefficient of expansion) of these materials. At the maximum of capacitance in a certain chip, size delamination is nearly unavoidable.

Now delamination may not be that catastrophic that we fear. If the capacitor is not subjected to extreme humidity that might diffuse into the cavities and the soldering is executed without any unsymmetrical heat conduction that may cause cracks in the ceramic we will never become aware of any delaminations (unless we deal with high voltage capacitors where the corona effect may be dangerous). It’s the authors’ opinion that only soldering with a soldering iron will cause such temperature gradients that the ceramic may crack. There are, however, other reasons why it may be advisable to avoid the highest capacitance values.

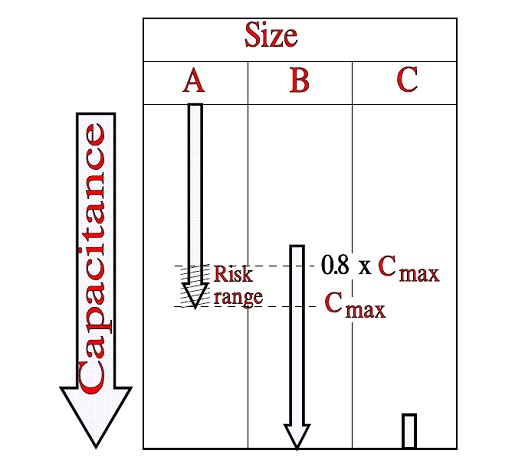

Figure 4. Rule of thumb for changing chip size.

The dielectric thickness, the number of electrode layers and the active capacitive area determine the capacitance in certain chip size. The thickness is varied by using one or several layers. But when we on the way towards higher capacitances pass from two to one layer the risk of short-circuit failures increases. It will, of course, be at a maximum when we pack the chip with the maximum number of layers. At the same time the risk of delamination increases. A practical limit where it may be advisable to avoid this twofold risk range by a size exchange is approximately 20% below the usually starts overlapping in next chip size (Figure 4 above).

If the component operates at high electric field strengths or in severe mechanical acceleration or chock environments we should in any case avoid maximum capacitance values in that size class, i.e. reduce the capacitance or increase the mechanical size.

We can also buy “high-rel” components, for example according to MIL-C-123 that specifies limits for the delamination extent and states methods for X-ray diagnosis. The price, however, will be approximately 20 times higher than that of a conventional standard component and the success with the X-ray check is debatable. Other methods with ultrasonics are developed but the result is many times difficult to interpret. Besides such equipment are expensive. In conclusion, only “space” and other “high rel” applications motivate the price we must pay for the increase in quality.

The burn-out process shouldn’t be forced too fast because of provoked delamination. On the other hand, it may not last too long. Then impermissible much of the palladium content of the electrode paste will oxidize. In other words, the time-temperature profile must be kept at an optimum level for the ceramic and electrode material.

After the burn-out process follows the considerably faster sintering of ceramic and electrode materials. Also here check of the time-temperature profile is extremely vital, not least the cooling time if we shall avoid micro-cracks in the ceramic.

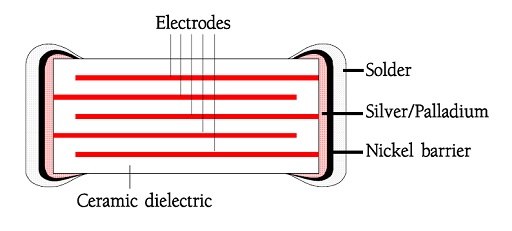

After the sintering terminations are applied which consist of

- farthest BME or Ag/Pd in good adhesion to the ceramic, 15…40 μm (0.6…1.6 mils)

- possibly a barrier layer (Ni) that will prevent silver from dissolving into the solder, 1…3 μm (0.04…0.1 mil) and

- farthest out Sn, 3…10 μm (0.1…0.4 mil) or solder, 10…100 μm (0.4…4 mils) (Figure 6).

If the inner electrodes consist of nickel or copper compatible termination materials have to be utilized. For that reason, nickel or copper based compounds are developed for outer terminations. They have a low migration and need only to be covered with a solderable alloy.

Electro-plating of tin as the outermost layer gives an evenly thick layer also on edges and corners. But because of a perpendicular orientation of the tiny crystals against the surface, they are leaving access to oxidizing oxygen if the tin layer is too thin. Therefore it should rather be 10 than 3 μm thick (0.4 mils rather than 0.1 mil). Hot or dip tinning creates a very tight layer but with uneven thickness. The covering on the corners becomes thin.

Figure 5. The spherical shape of a hot-tinned layer

Figure 6. A ceramic capacitor element with its termination metals.

Ceramic chips for surface mounting looks in principle like the one in Figure C2-74. Their physical sizes are decreasing. The most common EIA size is now (1998) 0402.

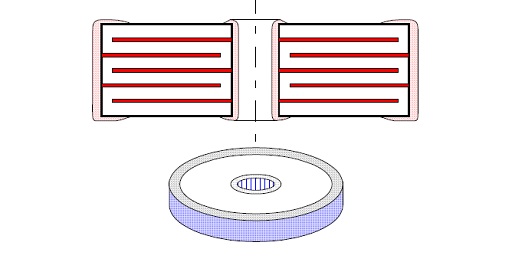

In filters and connectors, another chip variant occurs, the concentric one called discoidal.

Figure 7. Concentric chip (discoidal).

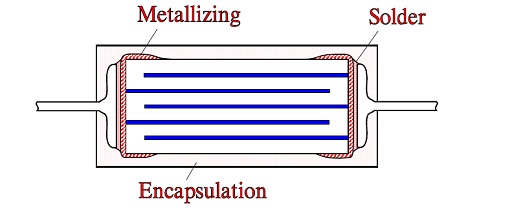

Lead mount components are supplied with leads and are encapsulated, for example, as in the following Figure 8.

Figure 8. Crosscut of an encapsulated ceramic MLC.

Failure Modes

Already during the construction report, we have touched on some of the failure modes that may appear in ceramic capacitors. Probably the most common one in MLCCs is short-circuiting at low voltage in high impedance circuits. It appears as micro-cracks in the ceramic. Under the influence of moisture and a polarizing voltage electrolytic material transportation from one electrode to the other easily takes place. We call it “ionic migration”.

We get a short-circuit that to its character resembles the one that may occur in carbon contaminated self-healing sites in plastic film capacitors. Similarly, the conductive path is extremely thin and is easily burnt away if the voltage exceeds certain minimum values. Should it, on the other hand, be too high we get a flash-over in the crack and this is hardly better.

It is well known that parts manufactured in older technologies had an increasing failure rate that started when the dielectric became thinner than 20…25 μm (» 0.8…1 mil). Even if some manufacturer’s technological progress has made the quality of thin dielectrics much better we still have to be cautious. The failure type is batch bound and manufacture dependent which among other things is connected with the sensitivity to dust and particles in the air.

Dielectric layers thinner than 50 μm (2 mils) require manufacture in clean rooms, i.e. rooms with filtered air and controlled number and size of particles. In other words, knowledge about good manufacturers is a must. Certainly, there are different methods to trace suspicious batches. In the so-called “85/85 test” according to MIL-C-123, the capacitors are exposed to 85% RH at +85°C and maximum 1.5 V DC in series with 100 kΩ for at least 240 hrs. But the efficiency of this test is not one-hundred-per-cent.

Another failure that above all strikes the common SMD components is bad solderability and silver leaching in more severe soldering processes. In order to meet the solderability problem, one ought to

- specify and check packaging method and component age and check the solderability in a wetting balance, at the relevant soldering temperature.

Hence storage of chips with their exposed terminations should be done in a protected environment. Above all, we should be on our guard for cardboard boxes because they may have a sulfur content which will cover silver alloys with a sulfide layer that destroys the solderability.

The leaching problem can be met with requirements for a barrier layer/nickel barrier. But a general requirement may not be enough. The freedom of pores in the nickel layer and its thickness is important. Besides also here knowledge about the manufacturers is necessary.

There are many pitfalls in the form of poor cleaning from plating bath residues, negligence with the oxidation protection of the nickel layer, etc. Finally, the soldering process might be quite unsuitable for nickel barrier designs. The streaming solder from the wave soldering rapidly conveys heat to the component surfaces and especially to the hard, fast-wetting nickel barrier. Long before the ceramic body has got warm the nickel layer has reacted with its thermal expansion.

In chips larger than 1210 this leads to the risk of cracks in the ceramic, inside the nickel barrier, especially if the layer is relatively thick. Therefore many leading manufacturers make larger sizes without any nickel barrier. But if we from serious manufacturers can find larger sizes with nickel barrier and they are not exposed to wave soldering but to the slower, more lenient processes like, for example, vapor phase, IR or hot air then chip sizes up to 2220 should be possible to use without any risk. Still larger sizes should have some kind of flexible terminals.

EPCI licensed content by:

[1] EPCI European Passive Components Institute experts original articles

[2] CLR Passive Components Handbook by P-O.Fagerholt*

*used under EPCI copyright from CTI Corporation, USA

- Space-Grade components available for immediate delivery - April 10, 2025

- Exclusive stock on doEEEt: How to access and request - April 10, 2025

- Managing EEE components for LEO and lower cost space missions - December 17, 2024

0 comments on Introduction to Ceramic Capacitors