MLCC and Ceramic Capacitors

- Posted by doEEEt Media Group

- On September 7, 2022

- 0

The article explains ceramic capacitors’ construction, manufacturing, application, and features.

Ceramic dielectric electrostatic capacitors are dominating the capacitor market in a number of fields:

- Largest volume capacitor technology (by far)

- Largest value capacitor technology

- Smallest dimension discrete components among all passives

- High flexibility of design to meet specific requirements such as low ESL / high-frequency operation

- Strong presence in both low voltage, low power and high voltage, high power applications

despite all the above benefits, the technology has some limitations that must be understood for the correct use and design-in. In the following chapters, we will also discuss two major groups of ceramic dielectric materials:

The basic construction types include simple – single-layer SLCC ceramic capacitors and major types made by stacking technology – MLCC multilayer ceramic capacitors.

Single layer ceramic capacitor SLCC

- simple construction

- low-cost technology

- lower CV

- higher ESR

- wide voltage range

- high voltage, high power applications

- RF/microwave applications

Wire bonded single layer ceramic chip in RF application

Multilayer MLCC ceramic capacitors

- mass volume

- miniaturization

- low ESR

- high CV

- flexible technology

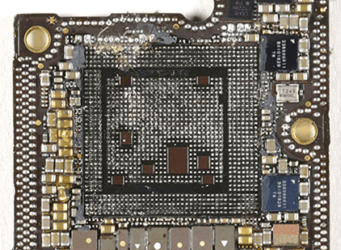

Example of high density MLCC on board of smartphone around and under the main processor (removed)

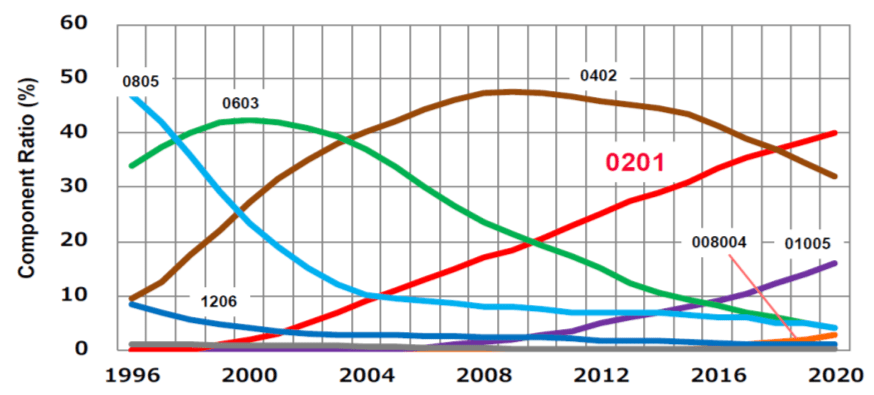

MLCCs chips are the leading downsizing and miniaturization technology among passive components. The chart below illustrates the shift of the case size mix in MLCCs. While the most popular case size in 1995 was 0805, 0603 in 2000, and 0402 in 2009, the most often used case size since 2018 is 0201, which is a capacitor in dimensions 0.6×0.3×0.3mm. The smallest MLCC in mass manufacturing is the 008004 cases introduced to volume production in 2019, with dimensions as small as 0.2×0.1×0.1 mm.

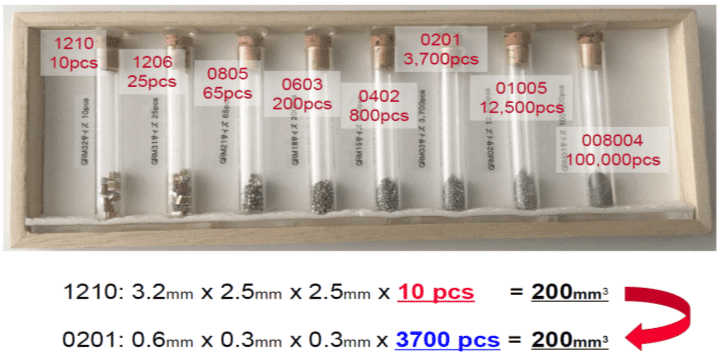

The enormous volumetric downsizing is illustrated in Figures 1. and 2. below – about the same volume taken by 10 pieces of 1210 case size is occupied by 100 000 pieces of 008004 capacitors!

Figure 1. MLCC ceramic capacitor case size share trend; source: Murata

Figure 2. MLCC ceramic capacitor case size volumetric comparison; source: Murata

Ceramic Dielectric Classifications

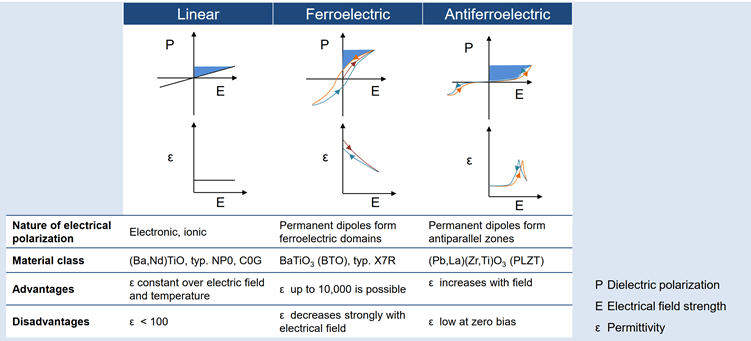

The different ceramic dielectric materials used for ceramic capacitors with linear (paraelectric), ferroelectric, relaxor-ferroelectric, or anti-ferroelectric behavior (Figure 3.) influence the electrical characteristics of the capacitors. Using mixtures of linear substances mostly based on titanium dioxide results in very stable and linear behavior of the capacitance value within a specified temperature range and low losses at high frequencies. But these mixtures have a relatively low permittivity, so the capacitance values of these capacitors are relatively small.

A specific group of materials is anti-ferroelectric dielectrics. In contrast to ferroelectrics, where permittivity decreases with applied voltage, antiferroelectric permittivity is low at low voltage and increases with electric field / applied voltage. These materials can achieve high CV and high capacitance at high voltage applications such as energy generation or EV/HEV vehicles in the automotive industry. See Figure 3. below for a comparison of polarisation curves between linear dielectrics (class 1), ferroelectrics (class 2), and anti-ferroelectric materials. We will discuss more in class 2. the ceramic capacitors chapter.

Figure 3. ceramic capacitors PE curves for linear, ferroelectric, and antiferroelectric dielectrics; source: TDK

Higher capacitance values for ceramic capacitors can be attained by using mixtures of ferroelectric materials like barium titanate together with specific oxides. These dielectric materials have much higher permittivities, but at the same time, their capacitance value is more or less nonlinear over the temperature range, and losses at high frequencies are much higher. These different electrical characteristics of ceramic capacitors require grouping them into “application classes.”

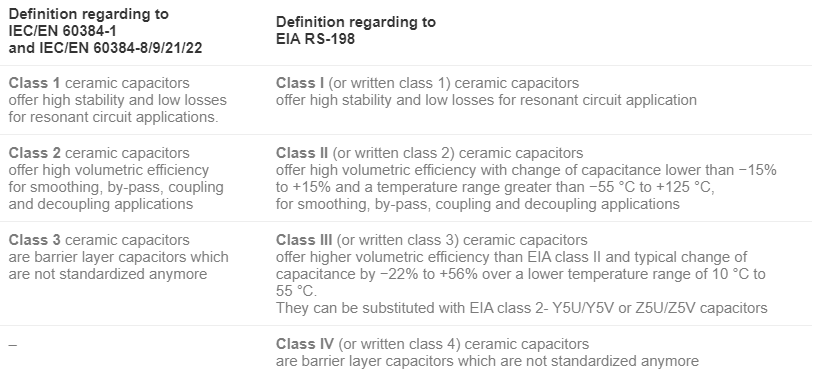

The definitions of the application classes given in the two standards are different. The following table shows the different definitions of the application classes for ceramic capacitors:

Table 1. Ceramic dielectric material classifications

Class I. (low loss, low capacitance density) and Class II are the most common. (high loss, high capacitance density) materials are discussed in the next chapters.

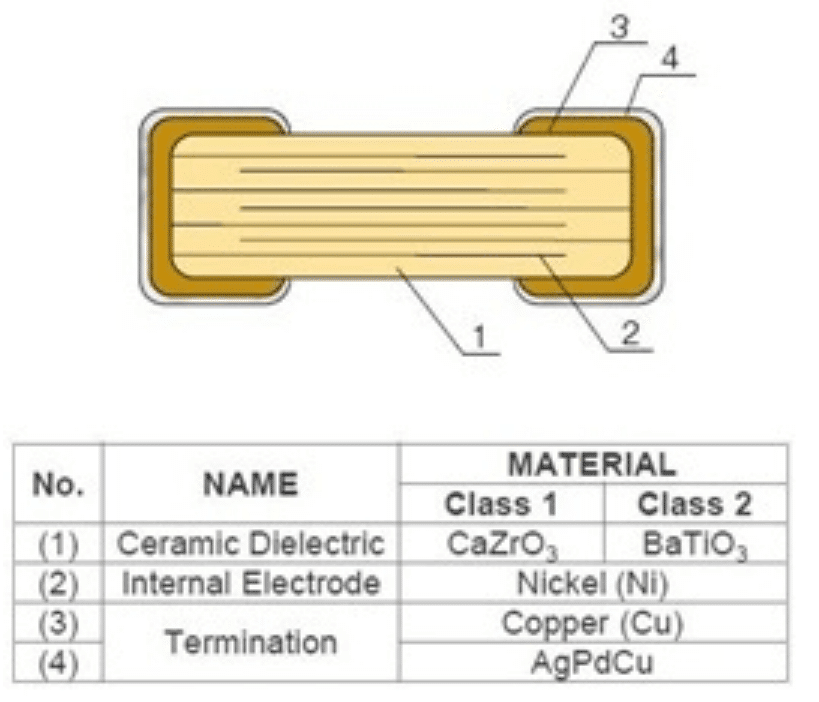

As the name tells us, the capacitors consist of some kind of ceramic. The manufacturing process starts with a finely grounded ceramic powder mixed with an emulsion of solvents and resin binders. In the first manufacturing step, the emulsion is dried to a soft film and screen printed with an electrode paste; historically, it was a compound of palladium or silver and palladium + binding agents. Due to the high cost of palladium, this termination style was replaced by metals like copper and nickel, so-called base metal electrodes (BME) that is a majority of today’s MLCC designs.

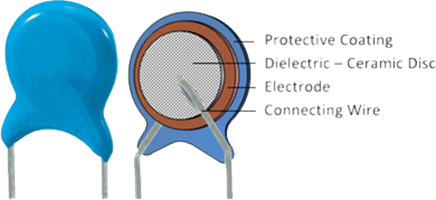

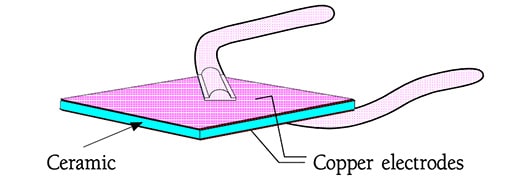

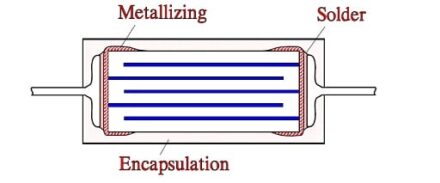

So-called tube capacitors are extruded out of a nozzle and are covered with an electrode paste on the inside and the outside before it’s sintered to their definite material structure. In the same way, the Single Layer Ceramic Capacitor (SLCC or just SLC) consists of one dielectric layer. The ceramic is covered with an adhesive layer of, for example, chrome nickel as a base for copper electrodes. On the electrodes, leads are soldered, as shown in Figure 5., before the component is encapsulated in lacquer or epoxy.

Figure 4. SLCC ceramic capacitors view; source: Vishay

Figure 5. Principle sketch of a single layer ceramic capacitor

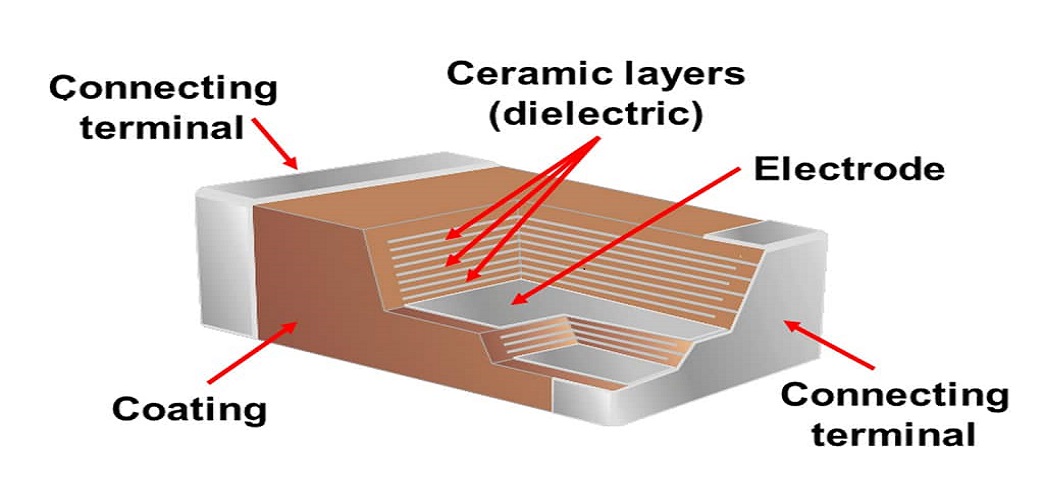

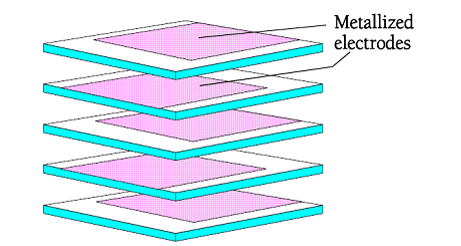

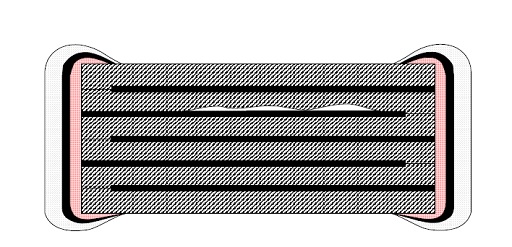

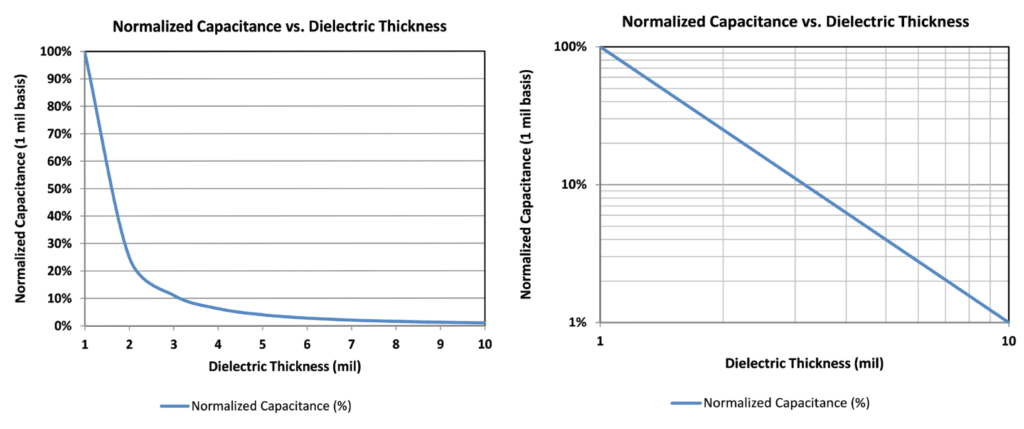

The most common ceramic capacitor design is the multi-layer construction where the capacitor elements are stacked, so-called MLCC (Multi-Layer Ceramic Capacitor). The number of layers has to be limited for the manufacturing technique. The upper limit amounts at present to over 1000. Besides, economic reasons come into play. On larger case sizes, stacking operation becomes less productive and raises the price steeply at higher capacitance values. The lowest capacitance values are achieved by only two layers, often separated by double ceramic layers.

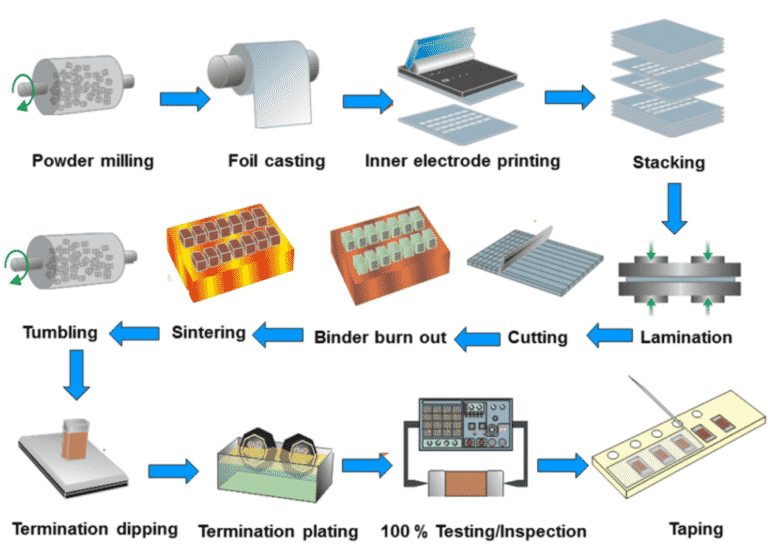

MLCC Manufacturing Process

In the conventional so-called dry method, the ceramic emulsion is dried on a conveyor belt before separating it from the supporting bed. After, it is cut into “primary sheets” that are screen printed with electrode paste for a large number of chips. These primary sheets are then stacked in an accurate steel frame and pressed to a solid piece to make it possible to cut out the separate chips from the stack with the electrodes in alternating positions.

In the latest variant of this method, one utilizes a conveyor film for the ceramic emulsion and has thus succeeded in reducing the dielectric thickness to 3 μm (0.1 mils). Here the quality implies manufacturing in extremely “clean rooms,” i.e., in rooms with filtered air and control of the number and size of particles.

Before the variant with a conveyor film was used in the dry method, the so-called wet method became increasingly common. The stage with the handling of “primary sheets” is skipped by letting the emulsion dry in “primary sheet frames.” In combination with better milling methods for the ceramic powder and a higher material purity, the wet method makes it possible with thinner dielectrics without a growing failure rate.

MLCC consists of several individual capacitors stacked parallel and contacted via the terminal surfaces. The starting material for all MLCC chips is a mixture of finely ground granules of raw materials modified by accurately determining additives. These powdered materials are mixed homogeneously. The mixture’s composition and the powder particles’ size, as small as 10 nm, reflect the manufacturer’s expertise.

Figure 6. MLCC ceramic capacitor manufacturing process; source: Wikipedia

A thin ceramic foil is cast from a powder suspension with a suitable binder. This foil is rolled up for transport. Unrolled again, it is cut into equal-sized sheets and screen-printed with a metal paste. These sheets become the electrodes. In an automated process, these sheets are stacked in the required number of layers and solidified by pressure. Besides the relative permittivity, the size and number of layers determine the later capacitance value. The electrodes are stacked in an alternating arrangement slightly offset from the adjoining layers so that they can later be connected on the offset side, one left, one right. The layered stack is pressed and then cut into individual components. For example, high mechanical precision is required to produce a 500 or more layer stack of size “0201” (0.5 mm × 0.3 mm).

After cutting, the binder is burnt out of the stack. This is followed by sintering at temperatures between 1,200 and 1,450 °C producing the final, mainly crystalline, structure. This burning process creates the desired dielectric properties. Burning is followed by cleaning and then metallization of both end surfaces. The ends and the inner electrodes are connected in parallel through metallization, and the capacitor gets its terminals. Finally, a 100% measuring of the electrical values will be done, and the taping for automated processing in a manufacturing device will be performed.

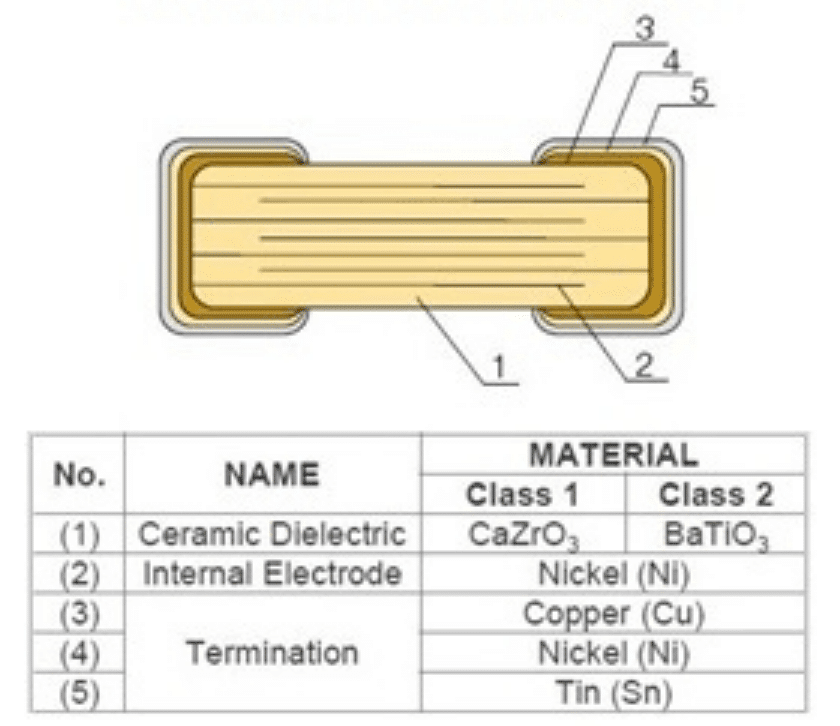

There are two basic termination structures – BME Base Metal Electrodes based on copper and nickel metals and PME Precious Metal Electrodes based on silver palladium metals. The original technologies mostly used PME structure, but palladium’s high prices pushed the industry to look for alternatives. The advantage of PME has been its TCE compatibility with the glass dielectric and, thus, lower stress during the firing process. However, BME is now the dominating structure and is subjected to the latest development. Thus, higher CV capacitors are available in BME configuration, while PME is used in mission-critical applications such as space or defense.

Figure 7. MLCC stacked MLCC capacitor construction

Figure 8. BME termination MLCC structure; source: TDK

Figure 9. PME (AgPd) termination MLCC structure; source: TDK

The separate cut loose chips are subjected to a first heat treatment (burn-out) where the organic binding agents – as part of the electrode paste – are gasified and diffused through the not-yet sintered ceramic. If this process is forced too fast, bubbles are formed that will separate electrodes and ceramics and result in so-called delaminations (Figure 10.).

Figure 10. Schematic of an MLCC ceramic capacitor delamination

Figure 11. Rule of thumb for changing chip size.

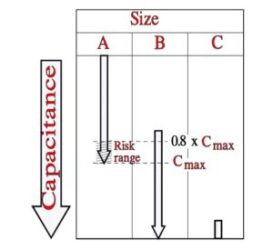

The dielectric thickness, the number of electrode layers, and the active capacitive area determine the capacitance in certain chip sizes. The thickness is varied by using one or several layers. But when we are on the way towards higher capacitances, passing from two to one layer, the risk of short-circuit failures increases. It will be at maximum when we pack the chip with the maximum number of layers. At the same time, the risk of delamination increases. A practical limit where it may be advisable to avoid this twofold risk range by a size exchange is approximately 20% below the usually starts overlapping in the next chip size (Figure 11. left).

The risk of delamination also increases with the number of layers. Primarily it depends on the quantity of electrode metal in the ceramic and the differences in TCE (coefficient of expansion) of these materials. At the maximum capacitance in certain chip sizes, delamination is nearly unavoidable.

Now delamination may not be as catastrophic as we fear. If the capacitor is not subjected to extreme humidity that might diffuse into the cavities and the soldering is executed without any unsymmetrical heat conduction that may cause cracks in the ceramic, we will never become aware of any delaminations (unless we deal with high voltage capacitors where the corona effect may be dangerous). The author believes that only soldering with a soldering iron will cause such temperature gradients that the ceramic may crack. However, there are other reasons why avoiding the highest capacitance values may be advisable.

If the component operates at high electric field strengths or in severe mechanical acceleration or chock environments, we should, in any case, avoid maximum capacitance values in that size class, i.e. reduce the capacitance or increase the mechanical size.

We can also buy “high-rel” components, for example, according to MIL-C-123, which specifies limits for the delamination extent and states methods for X-ray diagnosis. The price, however, will be approximately 20 times higher than that of a conventional standard component, and the success of the X-ray check is debatable. Other ultrasonic methods are developed, but the result is often difficult to interpret. Besides, such equipment is expensive. In conclusion, only “space” and other “high rel” applications motivate the price we must pay for the increase in quality.

The burn-out process shouldn’t be forced too fast because of provoked delamination. On the other hand, it may not last too long. Then impermissible much of the palladium content of the electrode paste will oxidize. In other words, the time-temperature profile must be kept at an optimum level for the ceramic and electrode material.

After the burn-out process follows the considerably faster sintering of ceramic and electrode materials. Also, a check off the time-temperature profile is extremely vital, not least the cooling time if we shall avoid micro-cracks in the ceramic.

After the sintering terminations are applied, which consist of…

- farthest BME or Ag/Pd in good adhesion to the ceramic, 15…40 μm (0.6…1.6 miles)

- possibly a barrier layer (Ni) that will prevent silver from dissolving into the solder, 1…3 μm (0.04…0.1 mils) and

- farthest out Sn, 3…10 μm (0.1…0.4 mils) or solder, 10…100 μm (0.4…4 miles)

If the inner electrodes consist of nickel or copper, compatible termination materials must be utilized. For that reason, nickel or copper-based compounds are developed for outer terminations. They have a low migration and must only be covered with a solderable alloy.

Figure 12. The spherical shape of a hot tinned layer

High Voltage SMT Ceramic Capacitors

Surface mount high voltage multilayer ceramic capacitors (HV MLCCs) appear to be pretty much identical to standard configuration MLCCs. They have the same basic form, fit, and function, but several key differences exist.

Typically, as a matter of definition, high voltage MLCCs have rated voltages that are greater than or equal to 200VDC. High voltage MLCCs are typically available in EIA sizes from 0603 to 2225 or larger (metric 1608 to 5664) with voltage ratings from 200V to 5,000V or more. Smaller case high voltage MLCCs typically have lower maximum rated voltages (VRated) as the external terminals tend to be closer than larger case high voltage MLCCs.

High voltage MLCCs are generally available with Class 1 (C0G) or Class 2 (e.g., Ferroelectric X7R) ceramic dielectrics with tolerances that are as good as +/-5% or better as wide as +/-20% or higher. Because of the generally thicker dielectric thicknesses used in the design and potentially the “cascade” or “floating electrode” type designs, the maximum capacitance values available are significantly lower than standard MLCCs.

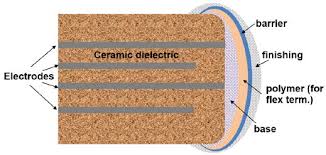

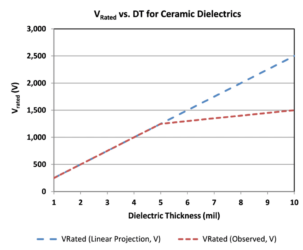

HVMLCCs appear similar to standard configuration MLCCs. It seems that it should be straightforward to design an HVMLCC of a given voltage rating; just keep increasing the dielectric thickness (DT) to enable the voltage rating desired, as you would with a standard configuration MLCC. The increase in DT is typically about 200 to 250 Volts per thousandth of an inch (V/mil, or ~7.8 to 10 V/μm).

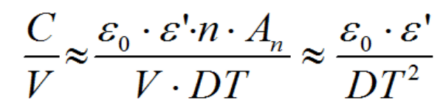

There is a penalty in capacitance per unit volume (C/V) using this approach to increasing rated voltage, as it requires increasing DT. The penalty in C/V is proportional to DT-2 following the relationship:

Standard MLCCs have no crack protection and are normally used for non-critical applications.

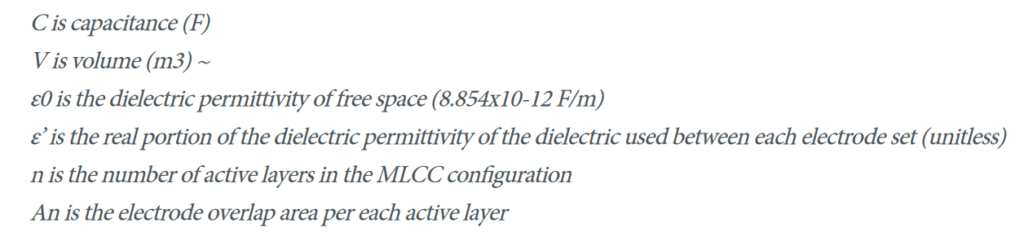

Soft termination (Flexiterm, Flexcrack, etc…, trade names) is based on the principle of introducing a soft, conductive layer (usually conductive polymer) to the MLCC terminals that absorb mechanical stress. See the figure on the right.

These capacitors can withstand up to 2-5mm of board flexure without internal cracks. Beyond 5mm, capacitors will generally fail “open,” Thus, this style is the preferred solution today for automotive and higher reliability applications.

Figure 13. MLCC ceramic capacitor soft termination (orange layer)

Electro-plating of tin as the outermost layer also gives an evenly thick layer on edges and corners. But because of a perpendicular orientation of the tin crystals against the surface, they leave access to oxidizing oxygen if the tin layer is too thin. Therefore, it should be 10 then 3 μm thick (0.4 mils rather than 0.1 mils). Hot or dip tinning creates a very tight layer but is unevenly thick. The covering on the corners becomes thin.

Flexible soft termination

Fail-Safe Multilayer Ceramic Capacitors (MLCCs)

Multilayer ceramic capacitors are highly susceptible to mechanical cracking due to their brittle nature. It is necessary for circuit board manufacturers to ensure that their board handling techniques do not expose boards to excessive bending (board flex) during manufacturing and operation. Some of the processes that can expose boards to excessive bending include mounting in assembling and depanelization. Unsupported input/output edge connectors and pick-and-place equipment can also cause excessive bending.

Figure 14. Approximate normalized capacitance vs. dielectric thickness (linear (left) and log-log (right)); source: Venkel

The above penalty in C/V as voltage rating is increased is not the only factor to consider; however, the above assumes that a constant rate of increase in DT is appropriate to achieve increased voltage rating. While this is true, typically to ~1,000 to ~1,500VRated ceramic dielectrics tend to deviate from that rate as VRated is increased above ~1,000 to ~1,500V, resulting in a different VRated vs. dielectric thickness relationship that is of the lower slope. A hypothetical example of this is given in the Figure below.

Figure 15. Dielectric thickness vs. rated voltage for a typical ceramic dielectric used in MLCCs; source: Venkel

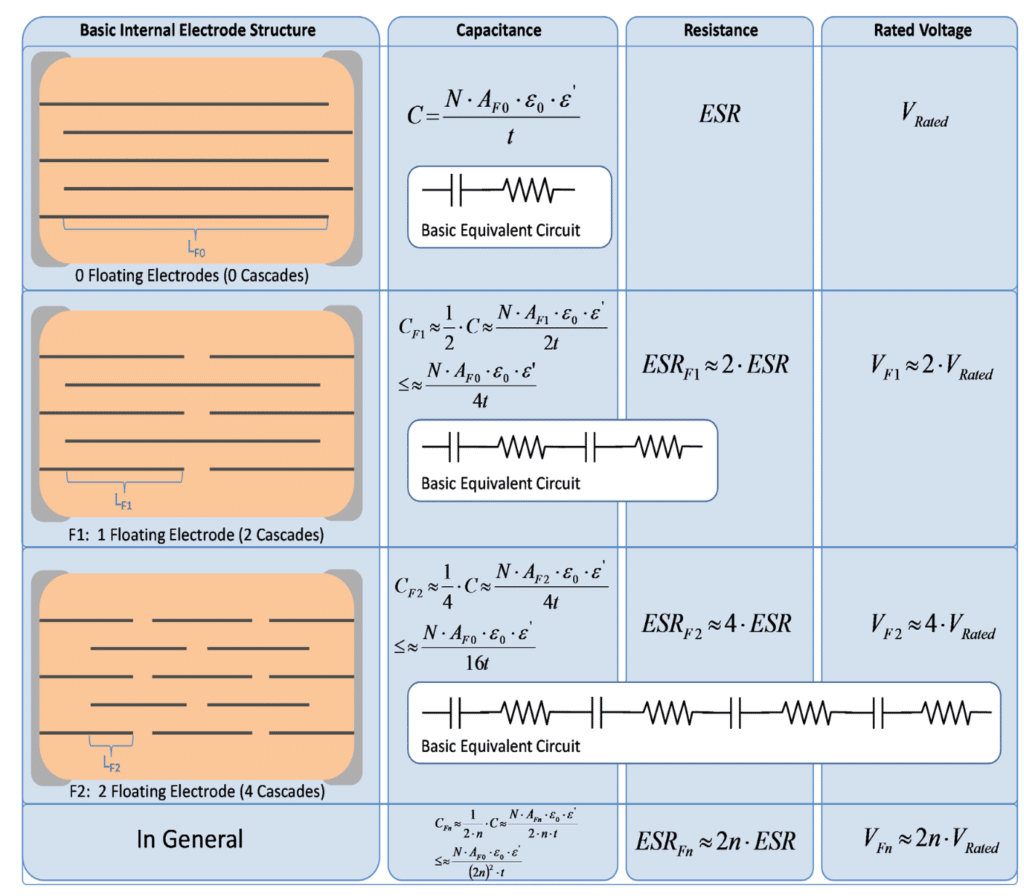

We can use floated electrodes (FE) or cascade electrode MLCCs to increase VRated with a relatively minimized impact on C/V as compared to standard configuration MLCCs at lower voltages (i.e., <~1,000V to ~1,500V). As each FE has an additional margin area associated with it, the impact of additional margins on C/V in small case MLCCs (typically EIA 0603 and 0805) may be prohibitive, but for larger MLCCs (e.g., EIA 1206 to 2225) the impact is acceptable to relatively small.

As in Figure 16. below, C/V decreases commensurately with (1/2n2), where n is the number of FEs within the design. VRated also increases with 2n, as does ESR. The effect on ESR is largely compensated for, however, as the two or more internal capacitors typically have more electrodes in each internal capacitor stack (N), thereby reducing ESR within each capacitor in series, and since the aspect ratio of said electrodes within each of the internal capacitors in series has relatively wide and short electrodes, which results in further decreased ESR. These two factors work together to reduce ESR such that the projected ESR increase is typically negligible and may even be reduced compared to standard configuration MLCCs of similar VRated.

Figure 16. Effects of floating internal electrodes on capacitance, ESR, and rated voltage; source: Venkel

Other Construction Types

RF Thin Film Ceramic Capacitors

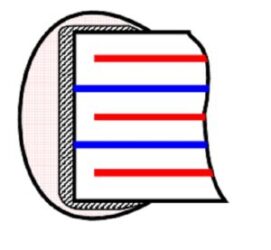

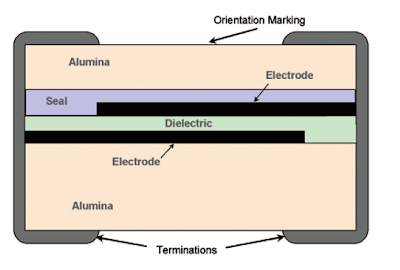

Thin-film ceramic capacitors use a single-layer low-loss ceramic dielectric packaged as a multilayer ceramic capacitor (MLCC) – see figure below. Its advantage is in very tight capacitance tolerance (even low batch-to-batch variation) and a single resonant point response. Thus such designs are ideal for RF and microwave filter designs.

Figure 17. thin film ceramic capacitor construction

A thin-film capacitor has an extremely repeatable frequency response compared to MLCCs.It is also important to realize the limitations of thin-film capacitors used as band-reject filters. Since thin-film capacitors are typically only available in low capacitance values, they are limited to relatively high-frequency band-reject filter designs. Other filter methods must be utilized when dealing with low-frequency designs, typically using high-Q multilayer RF capacitors.

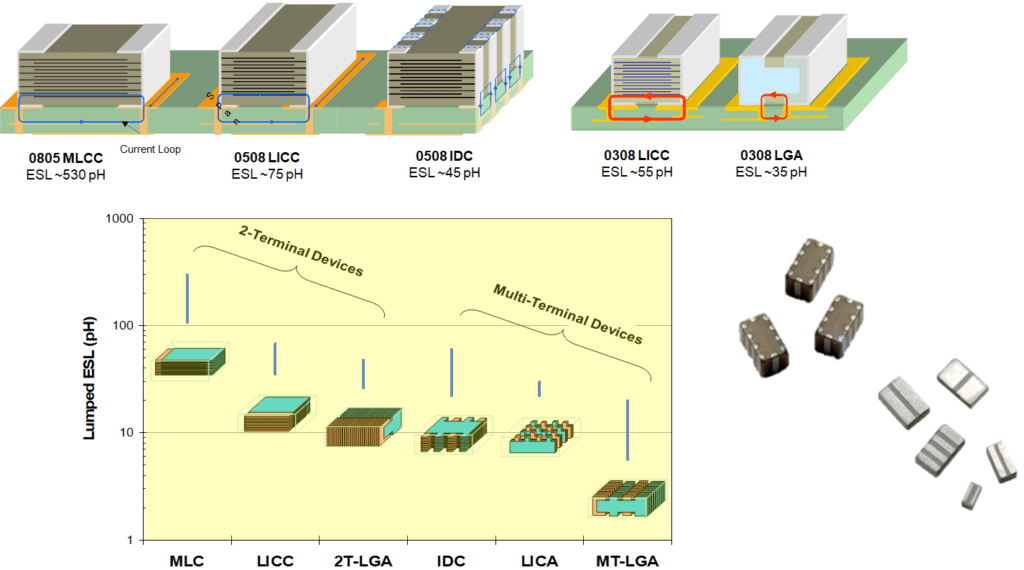

Low ESL designs

One of the key MLCC stacking technology advantages is its flexibility in electrode / dielectric layers layout. This allows a high customization level to match the technology with specific application field requirements. Low ESL, the high-frequency coupling is increasingly important with the latest generation of processors. The following figure illustrates a possible design configuration to reduce ECL and enable higher frequency operation.

Figure 18. MLCC ceramic capacitors low ESL design options; source: AVX

Lead mount MLCC

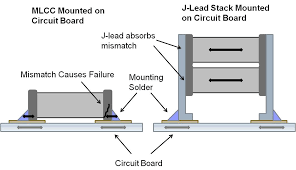

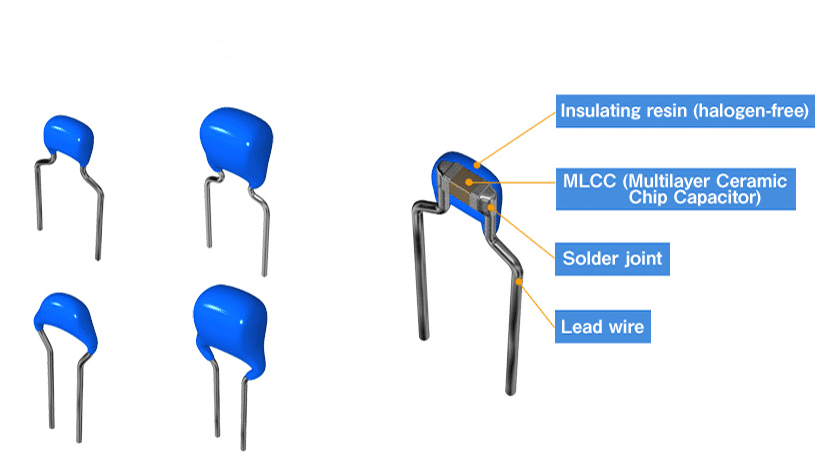

Lead mount components are supplied with leads. It can be encapsulated or stacked together by supported J-lead terminations, as in Figure 19.

The purpose of leaded MLCCs is not only to enable the technology for through-hole assembly but, in most cases, to reduce mechanical stress and the risk of cracking at larger case sizes. This is commonly used in high-rel industry or automotive to accommodate larger capacitance values while keeping high vibration robustness.

Leaded MLCCs; source TDK

Stacked MLCCs; source: TDK

Leaded stacked MLCCs; source Exxelia

Figure 19. encapsulated, leaded stuck MLCC ceramic capacitors

Discoidal

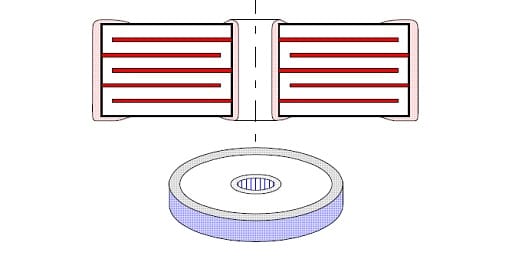

In filters and connectors, another chip variant occurs, the concentric one called discoidal, which is often used as a feedthrough capacitor.

Figure 20. Concentric chip (discoidal) feedthrough ceramic capacitors

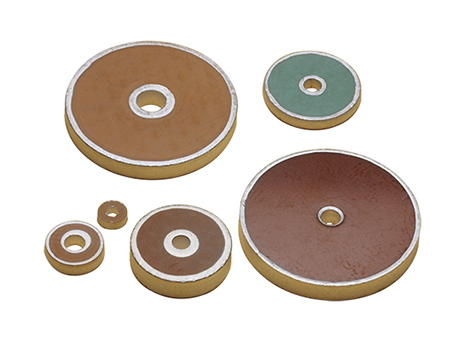

Figure 21. Discoidal feedthrough ceramic capacitors; source: API Technologies

Failure modes

Already during the construction report, we have touched on some of the failure modes that may appear in ceramic capacitors. The most common one in MLCCs is short-circuiting at low voltage in high impedance circuits. It appears as micro-cracks in the ceramic. Under the influence of moisture and a polarizing voltage, electrolytic material transportation from one electrode to the other easily takes place. We call it “ionic migration.”

We get a short circuit that, to its character, resembles the one that may occur in carbon-contaminated self-healing sites in plastic film capacitors. Similarly, the conductive path is extremely thin and is easily burnt away if the voltage exceeds certain minimum values. Should it, on the other hand, be too high, we get a flash-over in the crack, and this is hardly better.

It is well known that parts manufactured in older technologies had an increasing failure rate that started when the dielectric became thinner than 20…25 μm (» 0.8…1 mil). Even if some manufacturers’ technological progress has improved the quality of thin dielectrics, we still have to be cautious. The failure type is batch bound and manufacture dependent, which is connected with the sensitivity to dust and particles in the air.

Dielectric layers thinner than 50 μm (2 mils) require manufacture in clean rooms, i.e., rooms with filtered air and controlled number and size of particles. In other words, knowledge about good manufacturers is a must. Certainly, there are different methods to trace suspicious batches. In the so-called “85/85 test” according to MIL-C-123, the capacitors are exposed to 85% RH at +85°C and a maximum of 1.5 V DC in series with 100 kΩ for at least 240 hrs. But the efficiency of this test is not one-hundred-per-cent.

Another failure that strikes the common SMD components is bad solderability and silver leaching in more severe soldering processes. To meet the solderability problem, one ought to

- specify and check the packaging method, component age, and solderability in a wetting balance at the relevant soldering temperature.

Hence storage of chips with their exposed terminations should be done in a protected environment. Above all, we should be on our guard for cardboard boxes because they may have a sulfur content which will cover silver alloys with a sulfide layer that destroys the solderability.

The leaching problem can be met with requirements for a barrier layer/nickel barrier. But a general requirement may not be enough. The freedom of pores in the nickel layer and its thickness are important. Besides also here knowledge about the manufacturers is necessary.

There are many pitfalls in the form of poor cleaning from plating bath residues, negligence with the oxidation protection of the nickel layer, etc. Finally, the soldering process might be quite unsuitable for nickel barrier designs. The streaming solder from the wave soldering rapidly conveys heat to the component surfaces and especially to the hard, fast-wetting nickel barrier. Long before the ceramic body has gotten warm, the nickel layer has reacted with its thermal expansion.

In chips larger than 1210, this leads to the risk of cracks in the ceramic inside the nickel barrier, especially if the layer is relatively thick. Therefore many leading manufacturers make larger sizes without any nickel barrier. But if we from serious manufacturers can find larger sizes with nickel barrier and they are not exposed to wave soldering, but to the slower, more lenient processes like, for example, vapor phase, IR, or hot air, then chip sizes up to 2220 should be possible to use without any risk. Still, larger sizes should have some kind of flexible terminals.

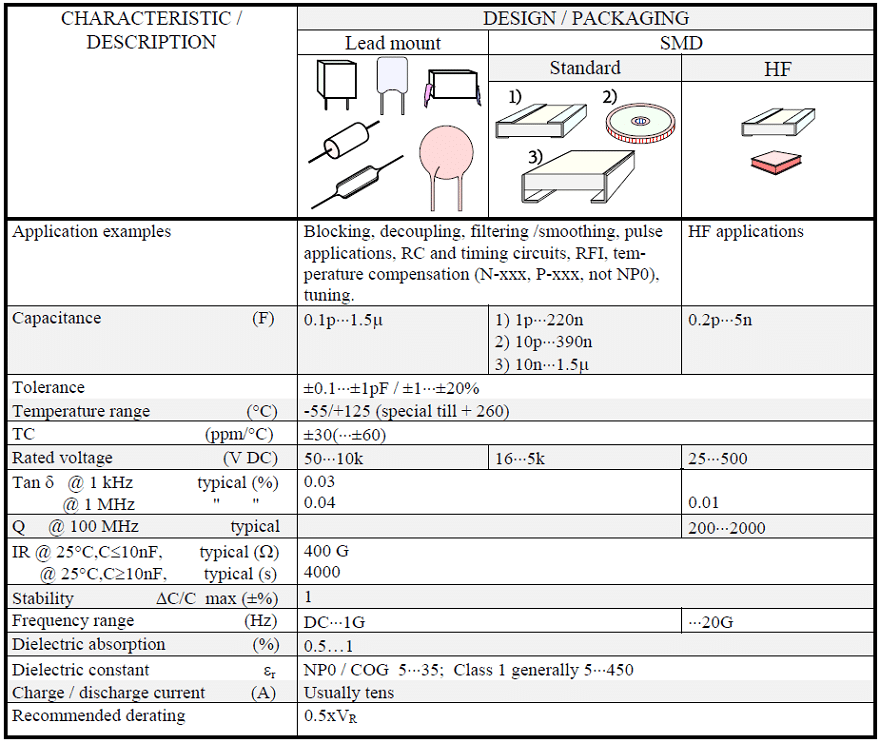

Capacitors Class 1 are manufactured using low loss linear paraelectric ceramic dielectric materials with low-temperature coefficients between +100 and –1500 ppm/°C. NP0 or COG (0 ± 30 ppm/°C) types are predominant over all remaining Class 1 variants.

To the Class 1 ceramics, we also count porcelain that is found in specific HF chips above all.

General comments to Class 1

The type is characterized by small losses, high IR, high stability, linear and moderate TCs between +100 and – 1500 ppm/°C, and an εr between 5 and 450. The tolerances range down to ±1%. Capacitances lower than 10 pF are challenging to produce to a percentage accuracy. The tolerances are instead stated in absolute values: ±0.1pF, ±0.25pF, ±0.5pF, and ±1pF.

At construction and failure analysis, you may sometimes find a pit in the ceramic of Class 1 capacitors. It may extend through all layers and is filled with some inert compound, often glaze. It is a so-called trim pit where part of the electrode surface is blasted away to match the capacitance value towards more acceptable tolerances, for example, 1 or 2%.

The ceramic mass shrinks enormously during the sintering – approximately 15% –and this may cause the capacitance distribution to get so skewed that it will be necessary to adjust it by trimming. The trim pits are harmless, provided the filling compound doesn’t contain blisters at the edge of adjacent layers.

The small losses in Class 1 ceramics do not correspond to a similarly low dielectric absorption. On the contrary, it is relatively high, approximately 0.5…1%.

The dielectric consists either of one layer – as a tube or in a plane shape, SLC from Single Layer Ceramics, or by several layers in stacked form, MLC from Multi-Layer Ceramics. In MLCs, the capacitance range is determined by the number of layers. At a minimum, it consists of one layer; at a maximum, it is limited by the manufacturing technique and for economic reasons. The noble metal AgPd paste of the electrodes is expensive; mostly, BME is a cheaper variant.

The temperature coefficient often is denoted by N(negative) or P(positive), followed by the value in ppm/°C. Here are some examples where we within brackets also mention the corresponding EIA designation:

- P100 = +100±30ppm/°C; (EIA = M7G)

- NP0 = 0±30ppm/°C; (EIA = COG)

- N150 = -150±30ppm/°C; (EIA=P2G)

- N1500= -1500±250ppm/°C; (EIA=P3K).

US MIL specifications have other designations.

In diagrams and tables, we henceforth confine ourselves to the predominant NP0/COG ceramic.

HF chips

When the frequency rises to some hundred MHz, conventional ceramics in MLC design start reacting with high and exponentially increasing losses. We come to a step on the way by modifying the ceramic. By passing to porcelain (εr = 12…15), which we include under the concept ceramics Class 1, the losses decrease sharply. Another way to reduce the HF losses is by passing to a single layer design, SLC, and introducing thin film electrodes in gold (Au), copper (Cu), or aluminum (Al). As a dielectric silicon dioxide (εr = 4.4) or silicon nitride εr = 7.5) is used.

Sometimes a changeover to a mica capacitor chip can reduce the losses.

The HF capacitors’ losses are expressed sooner in the quality factor Q (=1/tan δ) than in tan δ.

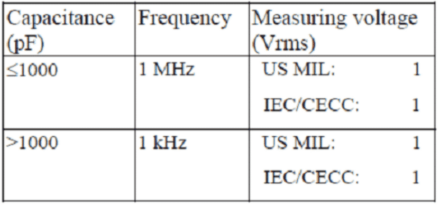

Measurement conditions

Table 2. Measurement conditions Class 1 ceramics

At IR and voltage strength tests sometimes in MIL and IEC/CECC, a charge and discharge limitation of a maximum of 50 mA is specified. Comments: These limitations probably are based on older manufacturing technologies. Some manufacturers nowadays have chosen to delete these requirements in their catalog sheets. Corresponding voltage rise times will for capacitances above 1 nF be unrealistically low. Such capacitors manage, according to performed tests, as a rule, at least 100 to 1000 times higher inrush currents, even at repetition frequencies in the kHz range.

Diagrams

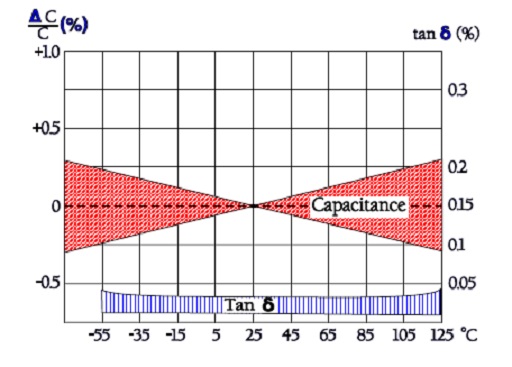

As usual, we shall present several diagrams describing the different temperature and frequency characteristics.

Temperature dependencies

Capacitance and Tan δ versus temperature

Figure 22. Class I ceramic capacitors capacitance and Tan δ versus temperature. Typical curve ranges for NP0/COG.

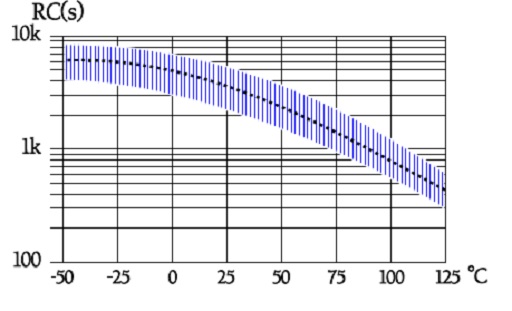

IR versus temperature

Figure 23. Class I ceramic capacitors typical curve range for IR versus temperature

Comments to Figure 23 about RC product and IR.

When we convert the RC product to insulation resistance (IR) expressed in MΩ and go down in capacitance, the IR increases correspondingly. Specifications usually set limits to the IR increase at 10 nF. According to the typical curve in the figure, RC is approximately 4000 s at 25°C, which gives an IR = 4000/10(nF) = 400 GΩ. Larger values can not be expected for capacitances lower than 10 nF.

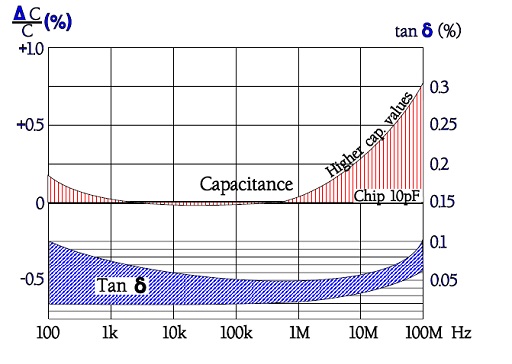

Frequency dependencies

Capacitance and Tan δ versus frequency

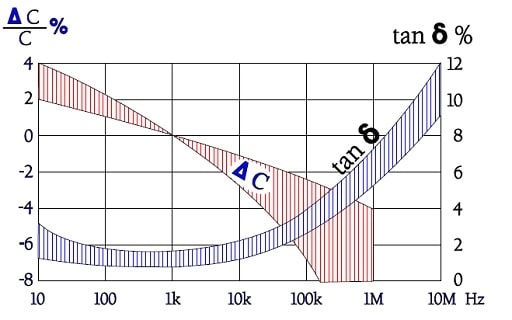

Figure 24. Class 1. ceramic capacitors Capacitance and Tan δ versus frequency. Typical curve range for NP0/COG.

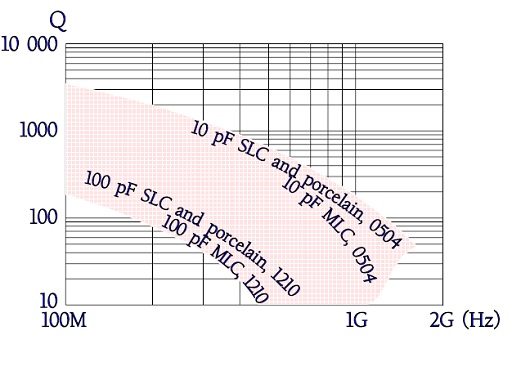

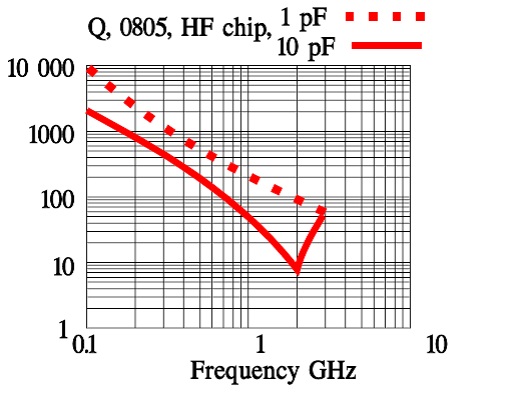

Q versus frequency

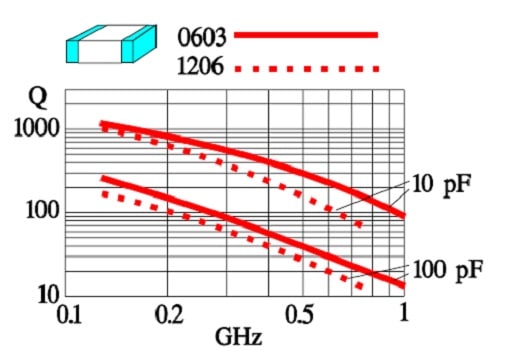

Figure 25. Information about Q value versus frequency for porcelain and ceramic class 1 ceramic capacitor chips.

Notice how the Q value increases with decreasing capacitance and chip size. Figures 25. and 27. show examples of the same phenomenon.

Figure 26. Example of class 1. ceramic capacitors Q value versus frequency.

Figure 27. Another example of class 1. ceramic capacitors Q value versus frequency and chip size.

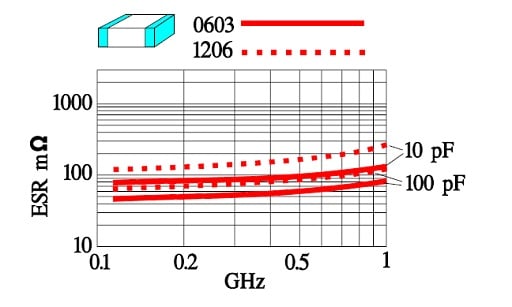

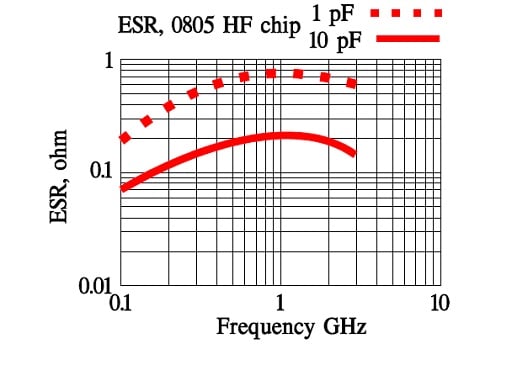

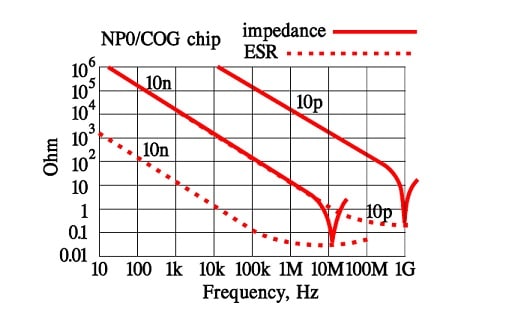

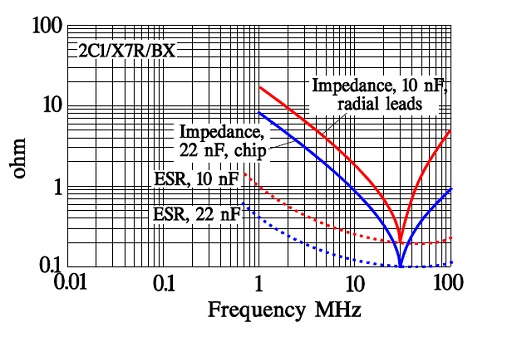

ESR for the same chip as in Figure 27. is shown in Figure 28. Other examples of the frequency dependence of ESR are found in Figures 29 to 31.

ESR versus frequency

Figure 28. Examples of class 1. are ceramic capacitors ESR versus frequency.

Figure 29. Another example of the class 1. ceramic capacitor ESR for 1 and 10 pF.

Figure 30. Class 1. ceramic capacitors ESR examples for 10 pF and 10 nF.

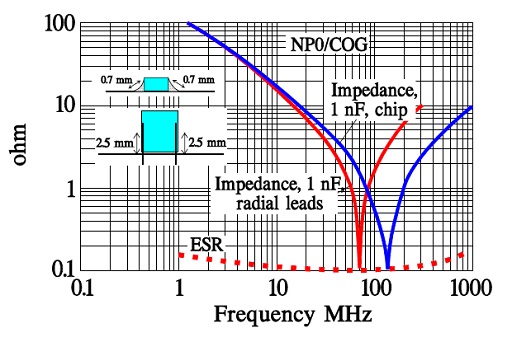

Figure 31. Examples of class 1. are ceramic capacitors ESR and impedance versus frequency in a chip and a lead mounted 1 nF capacitor.

Resonance frequency versus capacitance

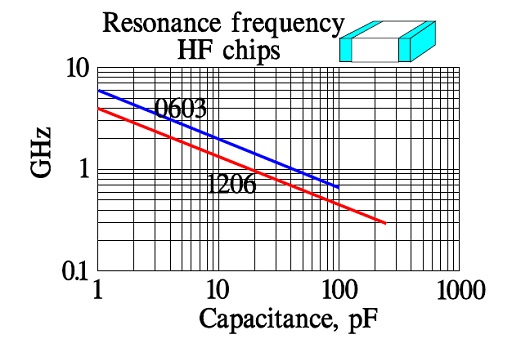

Examples of series resonance frequency versus capacitance for two sizes of HF chips in MLC design are shown below.

Figure 32. Examples of class 1. ceramic capacitors series resonance frequencies for HF chips in MLCC technique.

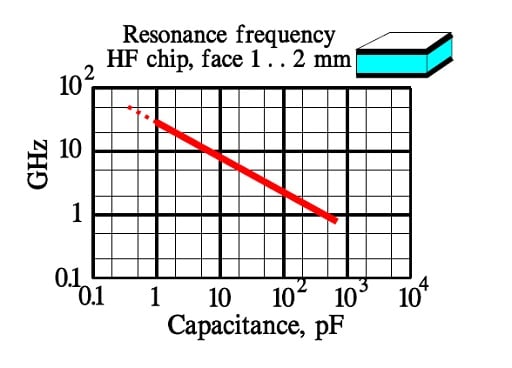

Figure 33. Example of class 1. ceramic capacitors resonance frequency in an SLCC chip.

As a comparison to the MLC example above, Figure 33. shows how a SLC chip in approximately the same size as 0603 may behave.

Table 3. CERAMICS CLASS 1 / NP0 / COG CHARACTERISTICS

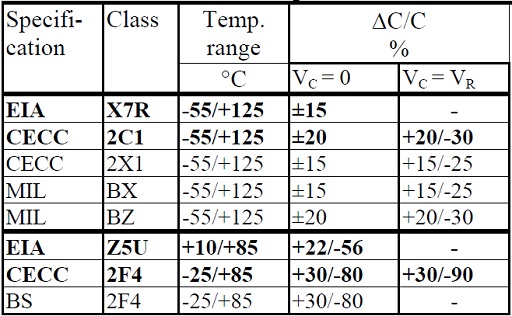

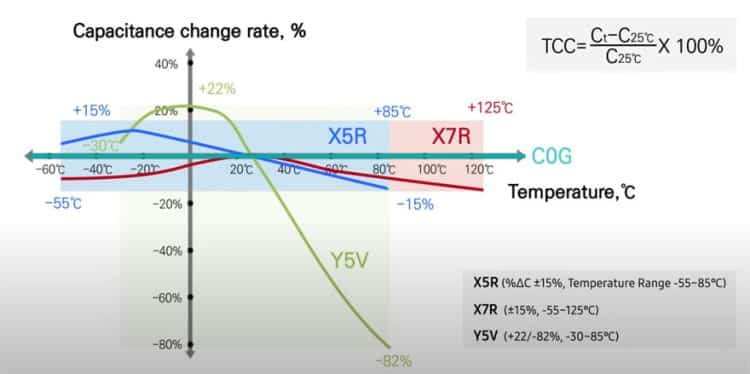

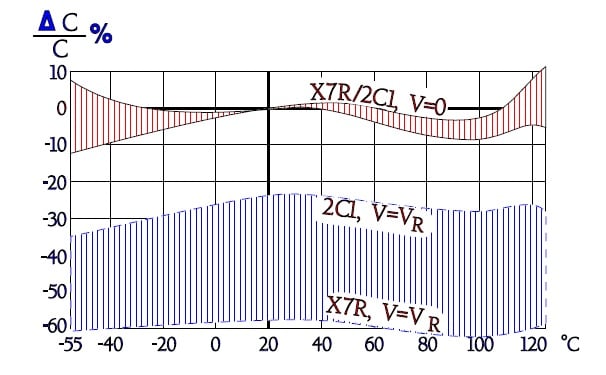

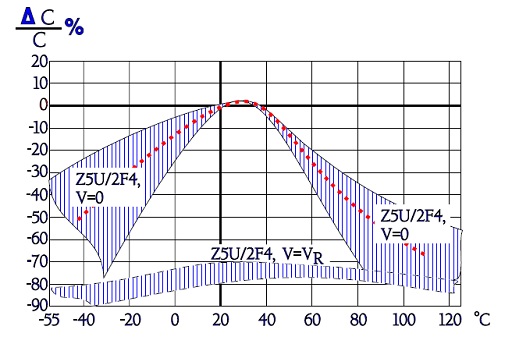

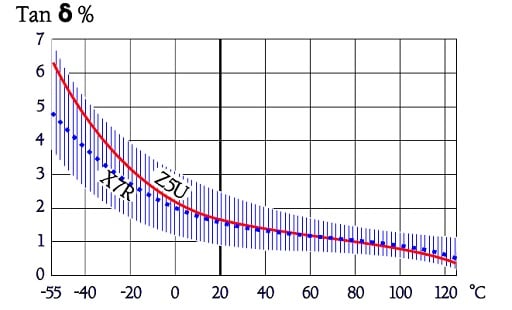

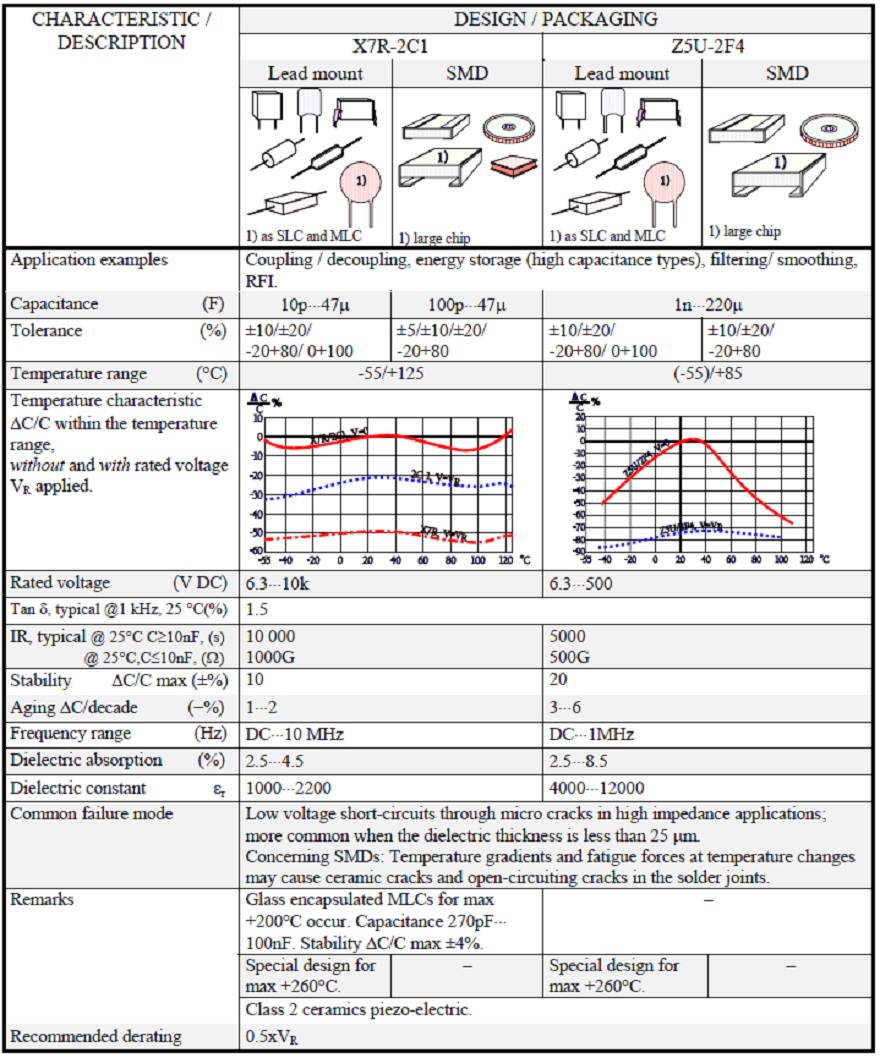

Ceramic Class 2 capacitors can be divided into two main groups, one with a moderate temperature dependence for the class – ΔC ≤ ±15% within the temperature range – and the other with such changes that only a fraction of the capacitance remains at the temperature limits. The first group is represented in our tables and diagrams by the ceramic type denominated X7R or 2C1, the latter by Z5U or 2F4.

Introduction to Class 2

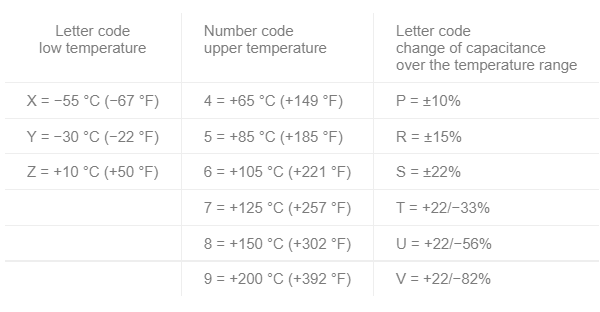

Class 2 capacitors are characterized by high dielectric constants, often designated with a K followed by the εr. Hence K2000 means εr ≈ 2000. The temperature dependence of the capacitance is large. Therefore EIA characterizes the ceramic with three characters that state the lower and the upper limit of the temperature range and last the capacitance change within the range.

Table 4. Ceramic capacitors EIA codes for temperature limits and capacitance changes, ΔC.

Example: X7R means with EIA designations the temperature range -55/+125 °C where the capacitance change maximum ±15%, provided the DC voltage is zero. The EIA code doesn’t consider that the Class 2 ceramic reacts with capacitance reduction to DC voltages.

On the other hand, certain other standards do. Here are some examples.

Table 5. Comparisons between ceramic capacitors classes. ΔC versus temperature and VDC.

Table 5. contains two main groups of Class 2 ceramics:

• K900⋅⋅⋅K2200; ΔC approximately ±20% within the temperature range.

• K4000⋅⋅⋅K12 000; very large ΔCs at the temperature limits.

There are within these groups many more materials, for example, the recent material Y5V, but in our diagrams and table information, we mostly will confine ourselves to X7R/2C1 and Z5U/2F4. By specification, Z5U is situated within a more limited temperature range than 2F4, but this has to do only with the specified ΔC, not with its capability to stand up to lower temperatures.

If we accept the capacitance changes caused by cold the ceramic will stand at -55°C. In the diagram section, we shall look closer at the temperature dependence of the capacitance. The upper-temperature limit, however, should not be exceeded. The capacitance tolerances for X7R usually are ±5, ±10, or ±20%. Usual Z5U tolerances are ±10, ±20 or -20/+80%. See also the figure below.

MLCC ceramic capacitor dielectric capacitance changes with temperature; source: Samsung Electro-Mechanics

The dielectric absorption is high:

• X7R/2C1 ≈ 2.5⋅⋅⋅4.5%;

• Z5U/2F4 ≈ 4.5⋅⋅⋅8.5%.

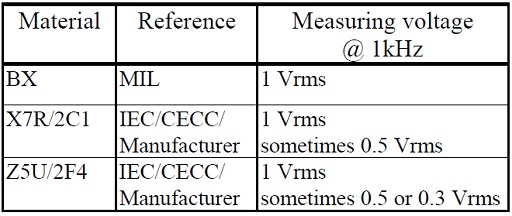

Measurement conditions

Table 6. class 2 ceramic capacitors reference measurement conditions.

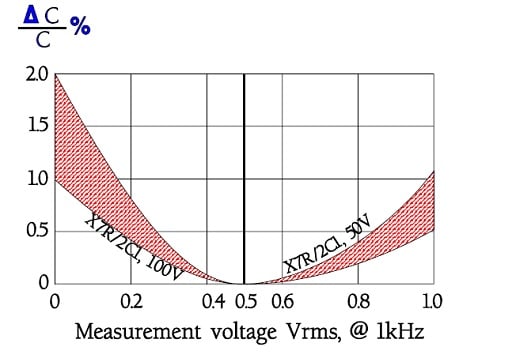

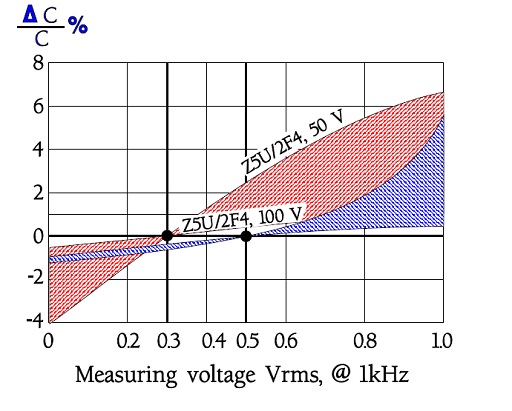

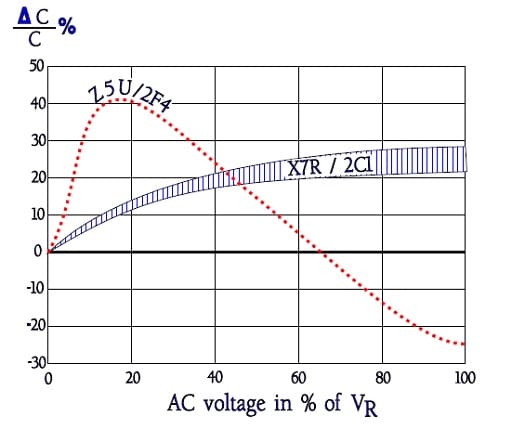

The measuring voltage is specified and limited depending on the capacitance, which changes with the applied alternating voltage. See examples in Figures 34 to 38.

Figure 34. Examples of class 2. ceramic capacitors ΔC versus measuring voltage for X7R/2C1 with different rated voltages

Figure 35. Examples of class 2. are ceramic capacitors ΔC versus electric tension for Z5U/2F4 with different rated and reference voltages.

The Curie temperature

Ceramic capacitors have a crystalline structure and dipoles that give the materials their unique dielectric constants εr. But the ceramic loses its dielectric properties above a certain brittle transition temperature, the so-called Curie temperature. The Curie temperature for Class 2 ceramics is usually between 125⋅⋅⋅and 150 °C. The influences don’t occur at any exact switch temperature but make themselves gradually discernible in the vicinity of the Curie temperature. Thus we should rather talk of the Curie range.

C 2.11.4 The dependence of capacitance on an applied voltage

Dielectric absorption (DA) and Ferroelectricity

The different types of Class 2 ceramics are based on barium titanates. Their crystalline structure is constituted by dipoles that present a dielectric hysteresis at the polarizing. With patterns from the hysteresis curve of magnetic materials, they are called ferroelectric.

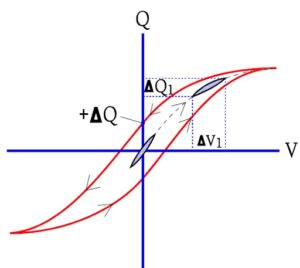

Figure 36. shows the capacitor charges versus the applied voltage.

Figure 36. Capacitor dielectric material with ferroelectric hysteresis.

When the voltage increases from zero to a limit value and then decreases, the charging curve follows another branch that at the voltage V = 0 leaves a residual charge + ΔQ. An alternating voltage of the same magnitude will force the charging curve along the outlines of the large hysteresis loop in the figure.

If the alternating voltage is small and the DC voltage = 0, the hysteresis loop will follow the small oval in the center of the figure. Small voltage changes correspond to large charge changes, i.e., high capacitance. But if we superimpose a small alternating voltage on a considerable DC voltage, we see how ΔV1 corresponds to fainter charge changes ΔQ1. The capacitance has dropped.

Figure 36. The ferroelectric material locks a residual charge ΔQ on the electrode surface when the voltage over the capacitor recedes to zero (outer circuit short-circuited). In other words, it’s a question of dielectric absorption (DA). But there is a difference, too.

The ferroelectric curve swings to the V axis while the general DA curve looks like a magnified picture of the center oval. In both cases, the bound residual charge ΔQ is time-dependent. If the outer circuit is short-circuited (V = 0), successively, charges on the electrode surfaces are set free while ΔQ decreases.

The ferroelectric energy absorption is polarity-dependent. Thus a complete re-polarizing will require more energy than the initial polarizing. But in, for example, D/A converters, the pulse time may not be sufficient for a satisfactory re-polarizing.

The considerable dielectric absorption in Class 2 ceramics makes them directly inappropriate for precision integrators like D/A converters, especially if there are positive and negative pulses. The crystalline structure of ferroelectric materials is maintained up to the Curie temperature.

A specific group of materials is anti-ferroelectric dielectrics, as we discussed in the introduction and Figure 3.

Piezo-electricity

If we expose a Class 2 ceramic material to electric field strength, it will cause faint movements in the ceramic. Inversely a mechanical pressure will create electric charges in the capacitor. The phenomenon is called piezoelectricity. BX ceramics (K900⋅⋅⋅⋅⋅⋅⋅⋅⋅K1800) exposed to chock/vibration produced in an experiment output voltages up to 40 mV3.

If we connect an X7R capacitor to an oscilloscope and bang a hammer on the component, we sometimes get high voltage spikes, sometimes not. It depends not only on how the blow hits but also varies from one sample to another. The output voltage is both manufacture and batch-dependent.

DC voltage dependence

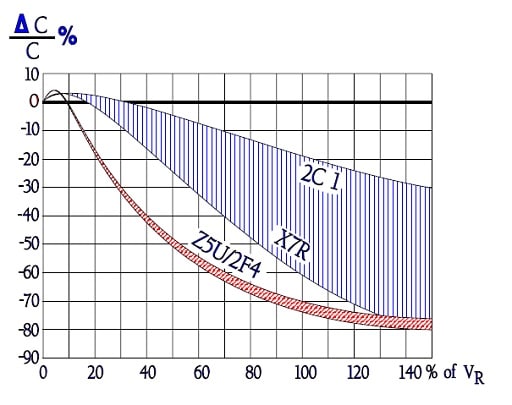

We showed just with reasoning around the ferroelectric curve how the capacitance decreased with an increasing DC voltage. How the DC voltage influences the capacitance is shown in Figure 37. Notice how specification requirements of voltage dependence affect, in other respects, equivalent materials.

For X7R, no requirements are called for – the dependence will be great –for 2C1, the dependence is maximized to –30%. Within the material classes, the voltage dependence increases with the rated voltage. The thickness of the dielectric, namely, doesn’t grow in proportion to the rated voltage. Thus, the electric field strength increases with increasing rated voltages, leading to a somewhat enhanced voltage dependence.

Figure 37. Typical curve range for ΔC versus DC voltage in different ceramic capacitor dielectric material classes

AC voltage dependence

Alternating voltages create a reverse effect than DC voltages on the capacitance.

Figure 38. Examples of ΔC versus AC voltage in percent of the rated voltage VR of class 2. ceramic capacitors.

Let us emphasize Figure 38. represent one example. Great variations may occur. In any case, norms’ significance for capacitance measurements is obvious. At IR measurements and voltage tests, MIL and IEC/CECC specify a charge and discharge limitation of a maximum of 50 mA.

Commentary: The limitations are questionable. Some manufacturers have chosen to delete these requirements in their catalog sheets. Some even specify voltage rise times of 1000V/μs, which for capacitances above 1 nF means surge currents ≥ 1A!

If your application requires considerable charge/discharge currents, please check with the manufacturer – or test for yourself – what the capacitor can stand and restrict the application to single pulses. Class 2 ceramics don’t stand an intense periodic pulse load.

Aging

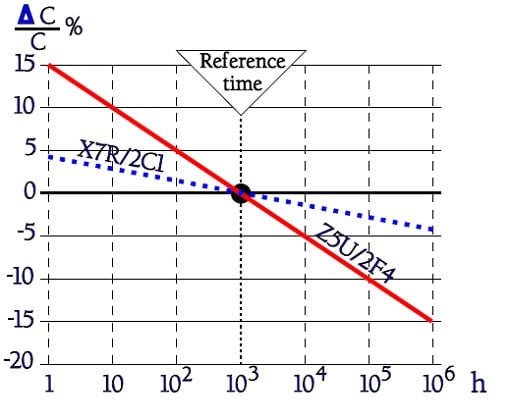

Class 2 ceramics lose capacitance with time. The decrease is called aging. It is conformable to a logarithmic law and decreases with a certain per cent per time decade.

Figure 39. Example of class 2. ceramic capacitors dielectrics aging diagram for X7R and Z5U ceramics.

In the diagram the capacitance of the Z5U ceramic decreases by approximately 6% per time decade and of the X7R ceramic by approximately 1.3%.

Typical aging constants usually are

• BX/X7R/2C1 1⋅⋅⋅2%

• Z5U/2F4 3⋅⋅⋅6%.

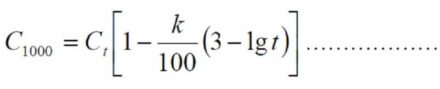

The aging constant k, expressed in percent per decade, follows the general formula.

The capacitance decrease is defined as starting 1 hour after cooling. To avoid disputes about delivered values, relevant norms state that the value shall be guaranteed at the 1000 hrs. With starting point from the formula, C2-2, the 1000 hrs value is then calculated as

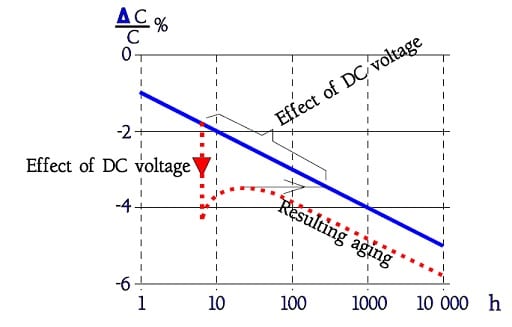

If a temporary DC voltage in the magnitude of VR is applied, there will be a lingering effect in the form of a capacitance decrease more or less as if the component had been aged for 1⋅⋅⋅1½ time decades (Figure 40.).

Figure 40. Aging effect from a momentary DC voltage in the magnitude of VR on class 2. ceramic capacitor dielectric

The figure also shows how the capacitance value increases to some extent when the DC voltage – here approximately VR – is removed.

The increase can amount to approximately

• +2.5% for C21 ceramics

• +5% for X7R and Z5U ceramics.

The aging starts by definition 1 hour after cooling. Now, if we heat a capacitor above the Curie point and let it cool, the crystal structures orientate themselves in the same way as after the manufacture, and the capacitance resumes its initial value before it, again, starts subsiding by the aging curve. One talks of “de-aging.”

Mind that every soldering of chip ceramics results in a damaging. De-aging effects may be evoked already in the lower part of the Curie range if the distance to the Curie point is compensated by a corresponding increase in time.

DC BIAS Ageing Effect

Ceramic class II capacitance loss with DC, AC, Temperature, and life might be multiplicated. To ensure the capacitor meets all requirements, attention must be paid to evaluating all operating conditions of the final electronic hardware. This is important, especially in mission-critical and safety applications.

Temperature dependence

Capacitance versus temperature and voltage

Figure 41. Typical curve range for class 2. ceramic capacitors capacitance versus temperature in X7R/2C1, with and without rated voltage applied.

Figure 42. Typical curve range for class 2. ceramic capacitors capacitance versus temperature in Z5U/2F4, with and without rated voltage applied.

Tan δ versus temperature

Figure 43. Typical curve ranges and average curves for class 2. ceramic capacitors dielectric Tan δ versus temperature in X7R/2C1 and Z5U/2F4

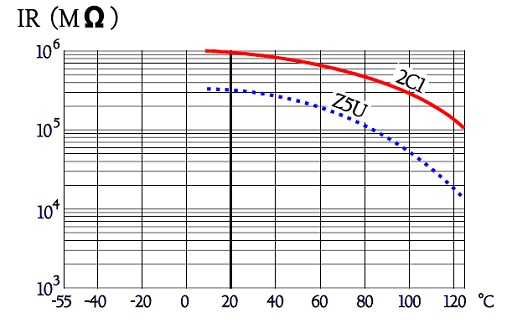

IR versus temperature

Figure 44. Typical examples of the IR versus temperature in class 2 ceramic capacitors chips.

The insulation resistance in Class 2 ceramic capacitors decreases with, on average, one power from room temperature to +125°C typically.

Frequency dependencies

Capacitance and Tan δ versus frequency

Figure 45. Typical curve ranges for capacitance and Tan δ versus frequency in X7R and 2C1 class 2. ceramic capacitors.

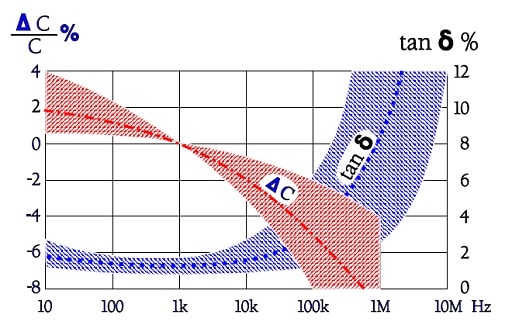

Figure 46. Typical curve ranges and average lines for capacitance and Tan δ versus frequency in Z5U / 2F4 class 2. ceramic capacitors dielectrics.

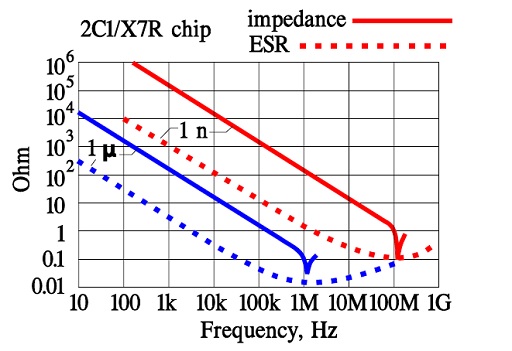

Impedance and ESR versus frequency

Figure 47. Examples of impedance and ESR versus frequency in X7R and 2C1 class 2. ceramic capacitors dielectrics

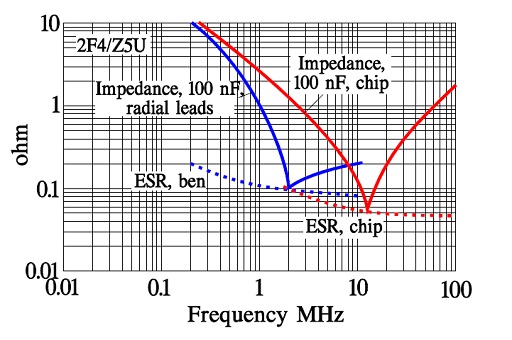

Figure 48. Examples of the frequency dependence of impedance and ESR in 2F4/Z5U class 2. ceramic capacitors dielectrics.

Figure 49. Other examples of the frequency dependence for impedance and ESR on class 2. are ceramic capacitors dielectrics.

Table 7. CERAMICS CLASS 2 / X7R-2C1 / Z5U-2F4 CHARACTERISTICS

Source: EPCI

- Space-Grade components available for immediate delivery - April 10, 2025

- Exclusive stock on doEEEt: How to access and request - April 10, 2025

- Managing EEE components for LEO and lower cost space missions - December 17, 2024

0 comments on MLCC and Ceramic Capacitors