Analog to digital converters: The resolution dilemma

- Posted by José Francisco Largaespada

- On April 19, 2020

- 0

We have been speaking lately about the data conversion stage of any electronic design and also about the components function upon all this stage is built: the analog to digital converters (ADC’s) and the digital to analog converters (DAC’s).

Once we have described the general characteristics of both types of components, we are going to focus in specific problems within the data conversion. In this case, we will deal with the difficulties of finding high resolution ADC’s for space applications. So far, in doEEEt platform are catalogued a bunch of ADC’s having 16 or more bits (the limit from which usually ADC’s are called “high resolution”). To be fair, this number needs to be reduced, because in some cases the differences from one reference to another is just the finish/package/quality level. This leaves us with a reduced effective different types of high-resolution ADC’s, and even less references available in the so called Space level.

So, to begin with, we need to recover some of the information that we gave in the entry about ADC’s. There, we defined resolution as the number of bits available at the output. From this, we can derive that resolution will stablish the minimum change in the analog input that can cause a change in the digital output. This is key, because thinking about it, at the end of the day, this will give an idea of the precision of the measurement. As an example, considering a ±500mV signal, the below table shows how the Least Significant Bit (LSB) varies with resolution, and since the 16-bit ADC can identify an interval as small as 15 µV , we can also imply that the digital representation of the 16-bit ADC would always be better than the one from the 8-bit[1]…or can’t we?.

[1] For the 8-bit any value between 0V and 3.92mV will be converted into the same digital number, whilst for the 16-bit the interval which gives the same digital number is 0V to 15 µV, thus making its representation better

| wdt_ID | Resolution | Minimum Voltage increment |

|---|---|---|

| 1 | 8-bit | 3.92 mV |

| 4 | 10-bit | 0.98 mV |

| 7 | 12-bit | 0.244 mV |

| 10 | 14-bit | 61 µV |

| 13 | 16-bit | 15 µV |

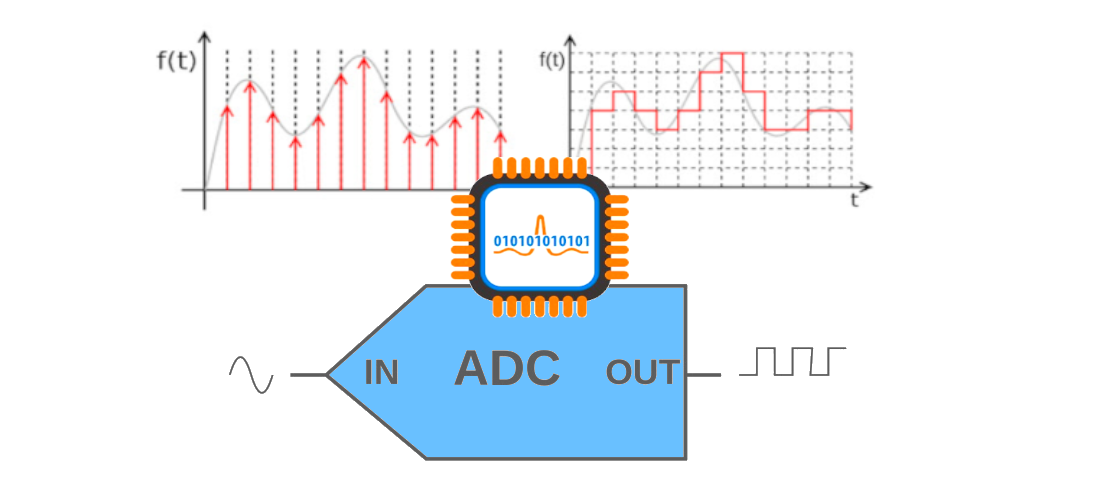

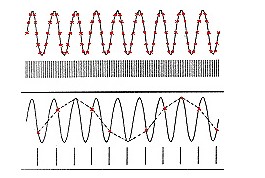

There is another parameter that is critical in the analog to digital conversion, which is usually a problem of high-resolution ADC’s, and that is the sampling rate. High resolution always pays the penalty of lower sampling rates, which can also derive in a poor representation of the analog signal, as it is shown in the next image.

As it can be seen, if the sampling rate is too slow compared to the frequency of the signal to convert, then what we get in the digital output does not resemble the original signal at all (lower figure of the image, dashed line is the sampled signal, solid line is the original signal). In fact, all this is well summarized in the Nyquist-Shannon theorem, which states that, in order finely sample a continuous signal, the sampling rate shall be twice the highest frequency in the signal.

With this brief information the main advantage and disadvantage of high-resolution ADC’s can be addressed: as an advantage there is the fact that they can resolve pretty well signals that include both small and high signal components; as a disadvantage we need to take into account that they have to work in low (or even very low) frequency applications.

Also, we would like to mention that, from the ADC architectures mentioned in the previous entry about ADC’s, the ones usually used for high-resolution ADC are pipeline and Sigma-Delta architectures.

- Plastic RT PWM and FET Driver from Renesas for New Space - June 5, 2022

- Component Selection in New Space Applications - July 2, 2021

- Product Assurance Plan for Small Sats - July 1, 2021

0 comments on Analog to digital converters: The resolution dilemma